# **INNOVATIVE FPGA CONTROLLER CARD FOR INVERTER SYSTEMS**

## ***DISSERTATION PHASE - II REPORT***

*Submitted by*

**MOHAMMED SHEHZAD K SALIM**

**Reg. No: MAC23ECVE05**

*to*

**APJ Abdul Kalam Technological University**

*In partial fulfilment of the requirements for the award of the Degree of*

**MASTER OF TECHNOLOGY

IN

VLSI AND EMBEDDED SYSTEMS**

**DEPARTMENT OF ELECTRONICS & COMMUNICATION

ENGINEERING**

**MAR ATHANASIUS COLLEGE OF ENGINEERING

KOTHAMANGALAM, KERALA, INDIA 686666**

**MAY 2025**

## **DECLARATION**

I Mohammed Shehzad K Salim hereby declare that the Dissertation Phase II report "Innovative FPGA Controller Card For Inverter Systems",submitted for partial fulfilment of the requirements for the award of the degree of Master of Technology of the APJ Abdul Kalam Technological University, Kerala is a bonafide work done by me under supervision of Dr.Mathew K and Prof.Mary Joseph. This submission represents my ideas in my own words, and where ideas of others have been included, I have adequately and accurately cited and referenced the original sources. I also declare that I have adhered to the academic honesty and integrity ethics and have not misrepresented or fabricated any data, idea, fact, or source in my submission. I understand that any violation of the above will be a cause for disciplinary action by the institute and/or the university and can also evoke penal action from the sources that have thus not been properly cited or from whom proper permission has not been obtained. This report has not previously formed the basis for the award of any degree, diploma, or similar title of any other university.

Place: Kothamangalam

Date: 19/05/2025

**MOHAMMED SHEHZAD K SALIM**

**DEPARTMENT OF ELECTRONICS & COMMUNICATION

ENGINEERING**

**MAR ATHANASIUS COLLEGE OF ENGINEERING

KOTHAMANGALAM**

**CERTIFICATE**

This is to certify that the Dissertation Phase II report entitled "**Innovative FPGA Controller For Inverter Systems**" submitted by **Mohammed Shehzad K Salim** to the APJ Abdul Kalam Technological University in partial fulfillment of the requirements for the award of the Degree of Master of Technology in the Department of Electronics and Communication is a bonafide record of the project carried out by him under my/our guidance and supervision. This report in any form has not been submitted to any other University or Institute for any purpose.

**Head of the Department**

Dr. Aji Joy

Professor

Dept. of ECE

**PG Coordinator**

Prof. Mary Joseph

Associate Professor

Dept. of ECE

**Project Guide**

Dr. Mathew K

Professor

Dept. ECE

**Faculty Advisor**

Prof. Nithin James

Assistant Professor

Dept. of ECE

## ACKNOWLEDGEMENT

First and foremost, I sincerely thank the 'God Almighty' for his grace for the successful and timely completion of the project.

I take this opportunity to express my deepest sense of gratitude and sincere thanks to everyone who helped me to complete this work successfully. I express my sincere gratitude and thanks to **Dr. Bos Mathew Jos**, our Principal, **Dr. Aji Joy**, Head of Department, **Prof. Mary Joseph** and **Prof. Nithin James**, Project Coordinators Electronics and Communication Engineering, Mar Athanasius College of Engineering, Kothamangalam for providing me with all the necessary facilities and support.

I would like to place on record my sincere gratitude to my project guide **Dr. Mathew K**, Professor, Electronics and Communication Engineering, Mar Athanasius College of Engineering for the guidance and mentorship throughout the course.

I express my sincere thanks to all the staff members in the Department of Electronics and Communication Engineering who have made sincere efforts to help me to complete this dissertation project

Finally I thank my family, and friends who contributed to the successful fulfilment of this project work.

MOHAMMED SHEHZAD K SALIM

## ABSTRACT

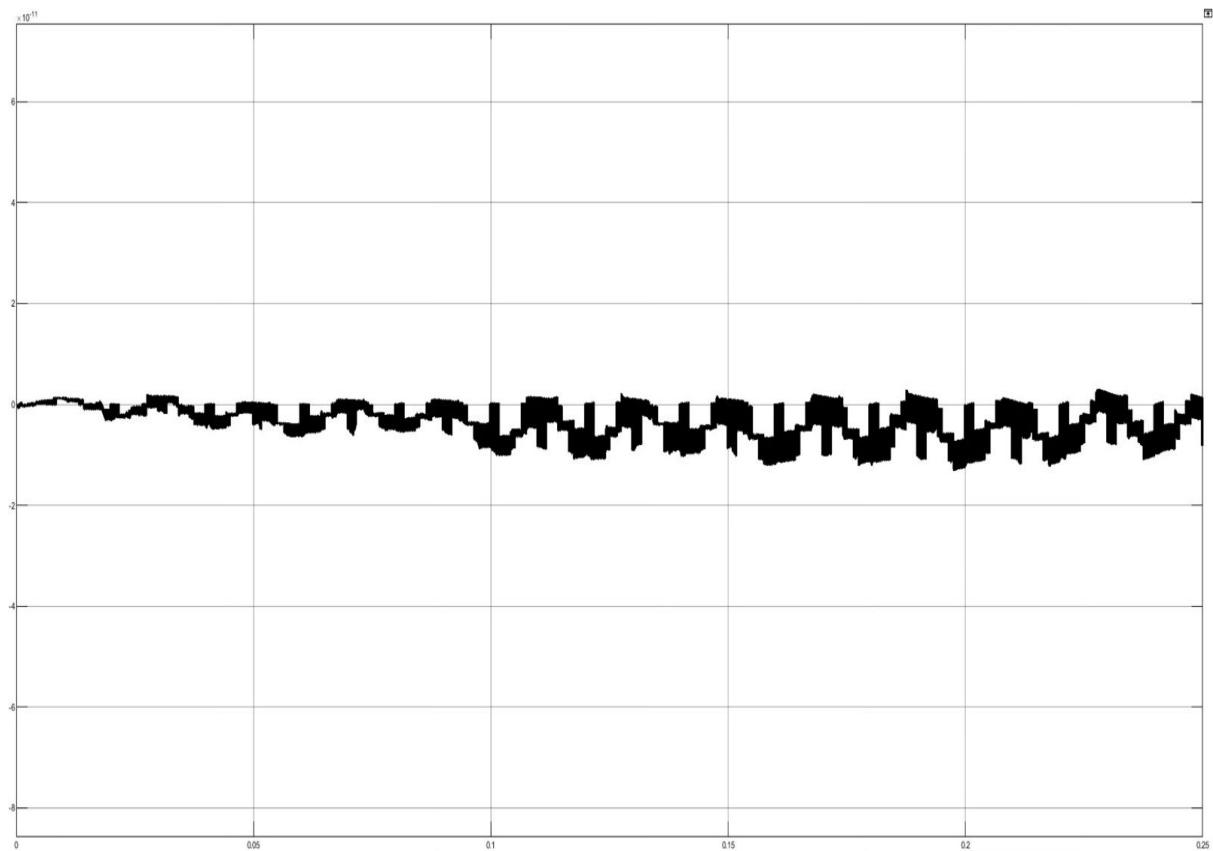

This dissertation presents the Phase II development of an FPGA-based controller for inverter systems that uses a two-level inverter topology. The controller leverages Sinusoidal Pulse Width Modulation (SPWM) to generate high-quality three-phase sinusoidal waveforms, ensuring efficient and reliable operation under varying load conditions. The hardware implementation, executed on the T20Q144I4 FPGA, successfully validates the SPWM output using an RC low-pass filter, which converts high-frequency switching signals into smooth sinusoidal waveforms. The proposed system demonstrates robust performance, maintaining stability under unbalanced load conditions 100% with minimal voltage regulation deviations. Furthermore, harmonic management techniques, including harmonic reduction and injection, ensure minimal Total Harmonic Distortion (THD). The controller supports variable output frequencies ranging from 40 Hz to 400 Hz and adjustable carrier frequencies, making it adaptable for diverse applications. Using the flexibility and processing speed of FPGA technology, the controller enables real-time adjustments and delivers optimal performance. The simplified two-level inverter architecture ensures ease of implementation while providing reliable power conversion. Phase 2 accomplishments establish a strong foundation for future developments, including advanced harmonic management, load optimization, and comprehensive operational enhancements, to achieve a versatile and efficient inverter control solution.

# TABLE OF CONTENTS

| <b>Contents</b>                                                                                                               | <b>Page No.</b> |

|-------------------------------------------------------------------------------------------------------------------------------|-----------------|

| <b>LIST OF FIGURES</b>                                                                                                        | <b>x</b>        |

| <b>1 INTRODUCTION</b>                                                                                                         | <b>1</b>        |

| <b>2 LITERATURE REVIEW</b>                                                                                                    | <b>2</b>        |

| 2.1 Paper 1 : FPGA Implementation of Multiple Single Phase PWM Inverters with Configurable Duty Cycle and Dead Time . . . . . | 2               |

| 2.2 Paper 2 : Implementation of FPGA-Based MSPWM Using 6-Input LUT for Reference Signal Generation . . . . .                  | 2               |

| 2.3 Paper 3 : Implementation in FPGA of an Alternative Modulation Strategy for Energy Balancing Purposes . . . . .            | 4               |

| <b>3 METHODOLOGY</b>                                                                                                          | <b>5</b>        |

| <b>4 DESIGN ASPECTS</b>                                                                                                       | <b>8</b>        |

| 4.1 Sinusoidal Pulse Width Modulation (SPWM) . . . . .                                                                        | 10              |

| 4.1.1 Unipolar SPWM . . . . .                                                                                                 | 11              |

| 4.1.2 Bipolar SPWM . . . . .                                                                                                  | 11              |

| 4.2 H-Bridge Topology in SPWM Inverter Systems . . . . .                                                                      | 12              |

| 4.3 Schematic Designing . . . . .                                                                                             | 15              |

| 4.3.1 Power Stage Architecture . . . . .                                                                                      | 15              |

| 4.3.2 Gate Drive and Control Signals . . . . .                                                                                | 17              |

| 4.3.3 Current Sensing . . . . .                                                                                               | 20              |

| 4.3.4 Sensing circuit for DC Link Voltage . . . . .                                                                           | 25              |

| 4.3.5 DC LINK TEMPERATURE SENSING CIRCUIT . . . . .                                                                           | 28              |

| 4.3.6 Phase Monitoring and Fault Detection . . . . .                                                                          | 31              |

| 4.3.7 DC Input Power Supply . . . . .                                                                                         | 34              |

| 4.3.8 Voltage Regulation . . . . .                                                                                            | 37              |

| 4.4 Component Selection Parameters . . . . .                                                                                  | 41              |

| 4.4.1 IGBT Selection (IKP40N65H5XKSA1) . . . . .                                                                              | 41              |

|                                    |                                                                          |           |

|------------------------------------|--------------------------------------------------------------------------|-----------|

| 4.4.2                              | Gate Driver IC (UCC21520DW) . . . . .                                    | 42        |

| 4.4.3                              | Gate Resistors (16.5Ω and 5.6Ω) . . . . .                                | 42        |

| 4.4.4                              | Snubber Capacitors (4.7nF) . . . . .                                     | 43        |

| 4.4.5                              | Current Sensing Shunt Resistors (0.005Ω) . . . . .                       | 43        |

| 4.4.6                              | Isolation Amplifiers (AMC1301DWVR and AMC1311DWVR) . . . . .             | 44        |

| 4.4.7                              | Voltage Divider Resistors for DC Link Sensing . . . . .                  | 44        |

| 4.4.8                              | NTC Thermistor Interface Circuit . . . . .                               | 45        |

| 4.4.9                              | Operational Amplifiers (OPA320AIDBVR) . . . . .                          | 45        |

| 4.4.10                             | Comparators (TLC372QDRG4) . . . . .                                      | 45        |

| 4.4.11                             | Low-Dropout Regulator (TLV1117-331DCYR) . . . . .                        | 46        |

| 4.4.12                             | Filtering Capacitors . . . . .                                           | 46        |

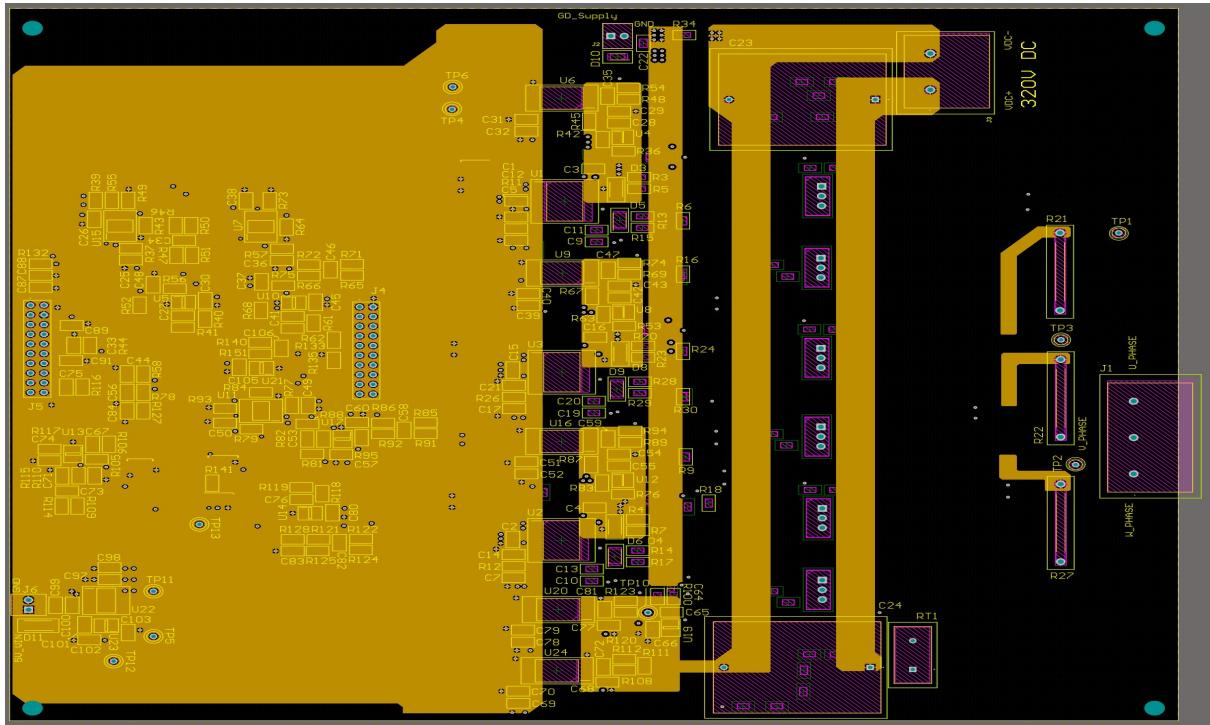

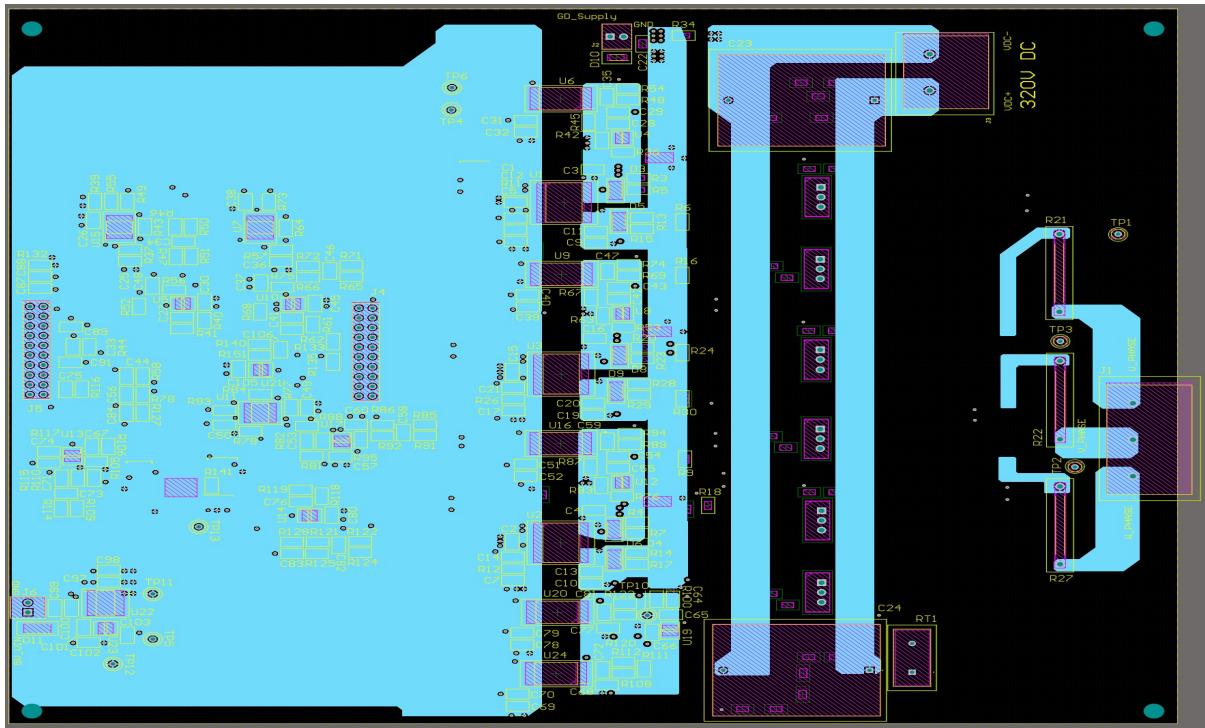

| 4.5                                | PCB Designing . . . . .                                                  | 47        |

| 4.6                                | Design Rules . . . . .                                                   | 56        |

| 4.7                                | Control System Architecture . . . . .                                    | 62        |

| <b>5</b>                           | <b>EXPERIMENTS &amp; SIMULATIONS</b>                                     | <b>66</b> |

| 5.1                                | Analysis Analysis of Three-Phase Inverter Simulation Waveforms . . . . . | 69        |

| 5.2                                | Hardware implementation of Three phase spwm implementation . . . . .     | 75        |

| <b>6</b>                           | <b>CONCLUSION</b>                                                        | <b>77</b> |

| <b>7</b>                           | <b>REFERENCES</b>                                                        | <b>79</b> |

| <b>A</b>                           | <b>Appendix A: Sine Look Up Table Code</b>                               | <b>82</b> |

| <b>B</b>                           | <b>Appendix B: Sine Wave Generator Code</b>                              | <b>83</b> |

| <b>C</b>                           | <b>Appendix C: Carrier Wave Generator</b>                                | <b>84</b> |

| <b>D</b>                           | <b>Appendix D: Single Phase SPWM Generator</b>                           | <b>85</b> |

| <b>E</b>                           | <b>Appendix E: Three Phase SPWM Generator</b>                            | <b>87</b> |

| <b>Appendix G: Current Sensing</b> |                                                                          | <b>89</b> |

| <b>Appendix G: Current Sensing</b> |                                                                          | <b>90</b> |

**Appendix H: Voltage Sensing** **91**

**Appendix I: Pin Configuration** **92**

## LIST OF FIGURES

|      |                                                                   |    |

|------|-------------------------------------------------------------------|----|

| 3.1  | The Proposed System . . . . .                                     | 5  |

| 3.2  | The Proposed Inverter Design . . . . .                            | 6  |

| 4.1  | H - Bridge Topology . . . . .                                     | 13 |

| 4.2  | H - Bridge Design . . . . .                                       | 15 |

| 4.3  | Gate Driver Design . . . . .                                      | 17 |

| 4.4  | Current Sensing Circuit . . . . .                                 | 21 |

| 4.5  | DC Link Voltage Sensing Circuit . . . . .                         | 25 |

| 4.6  | DC Link Voltage Sensing Circuit . . . . .                         | 29 |

| 4.7  | Phase Monitoring and Fault Detection Circuit . . . . .            | 32 |

| 4.8  | DC Power Supply Circuit . . . . .                                 | 34 |

| 4.9  | Voltage Regulation Circuit . . . . .                              | 38 |

| 4.10 | Layer Stack Managing and Material Selection . . . . .             | 47 |

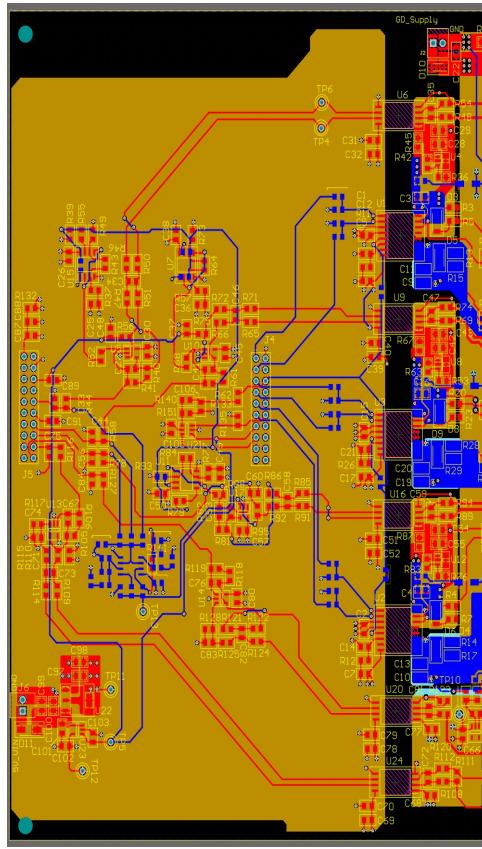

| 4.11 | Designing ground planes . . . . .                                 | 49 |

| 4.12 | Designing power planes . . . . .                                  | 50 |

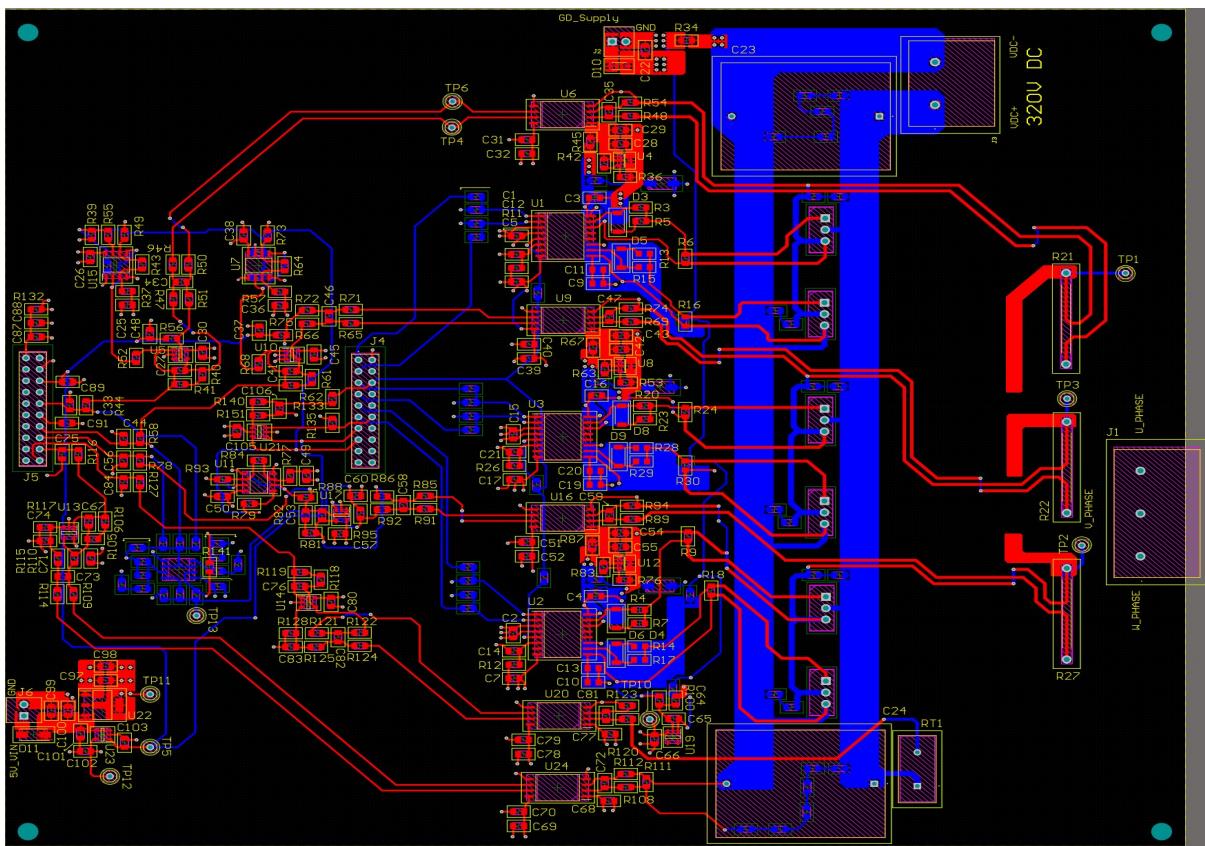

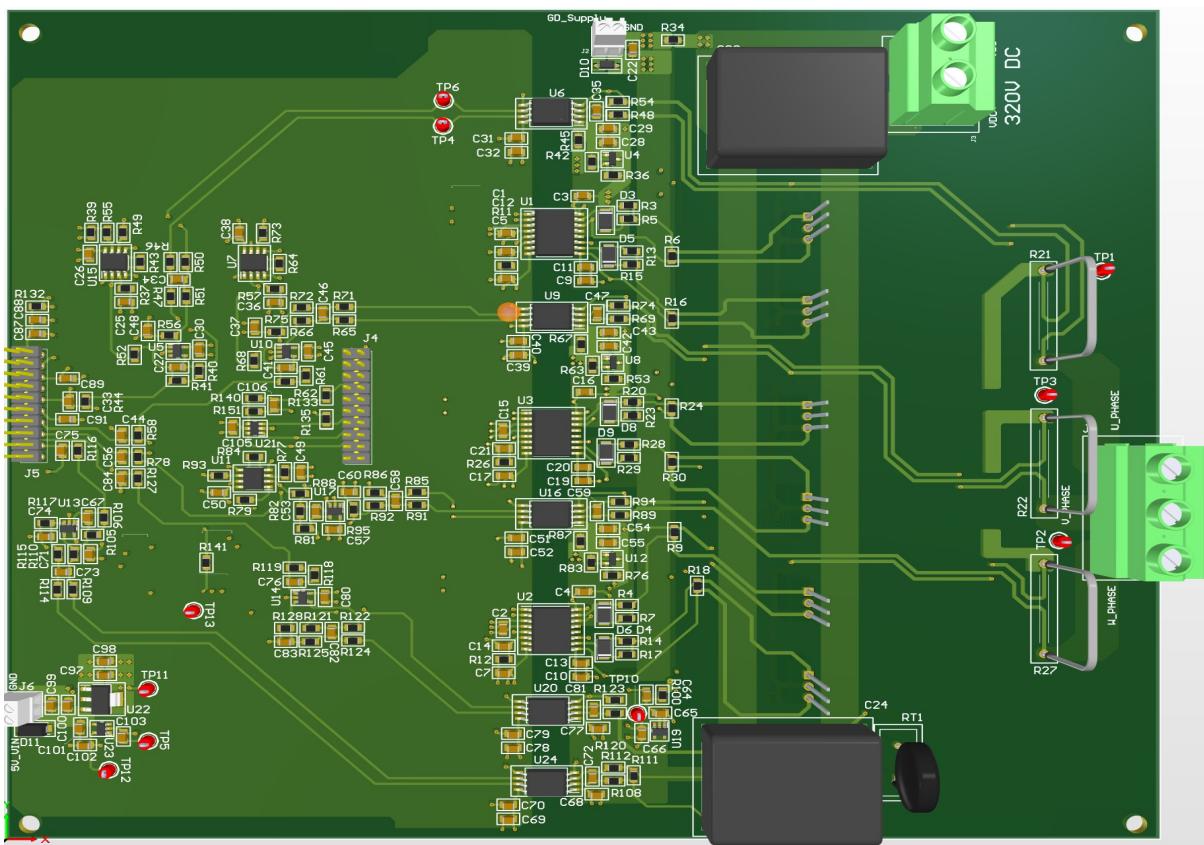

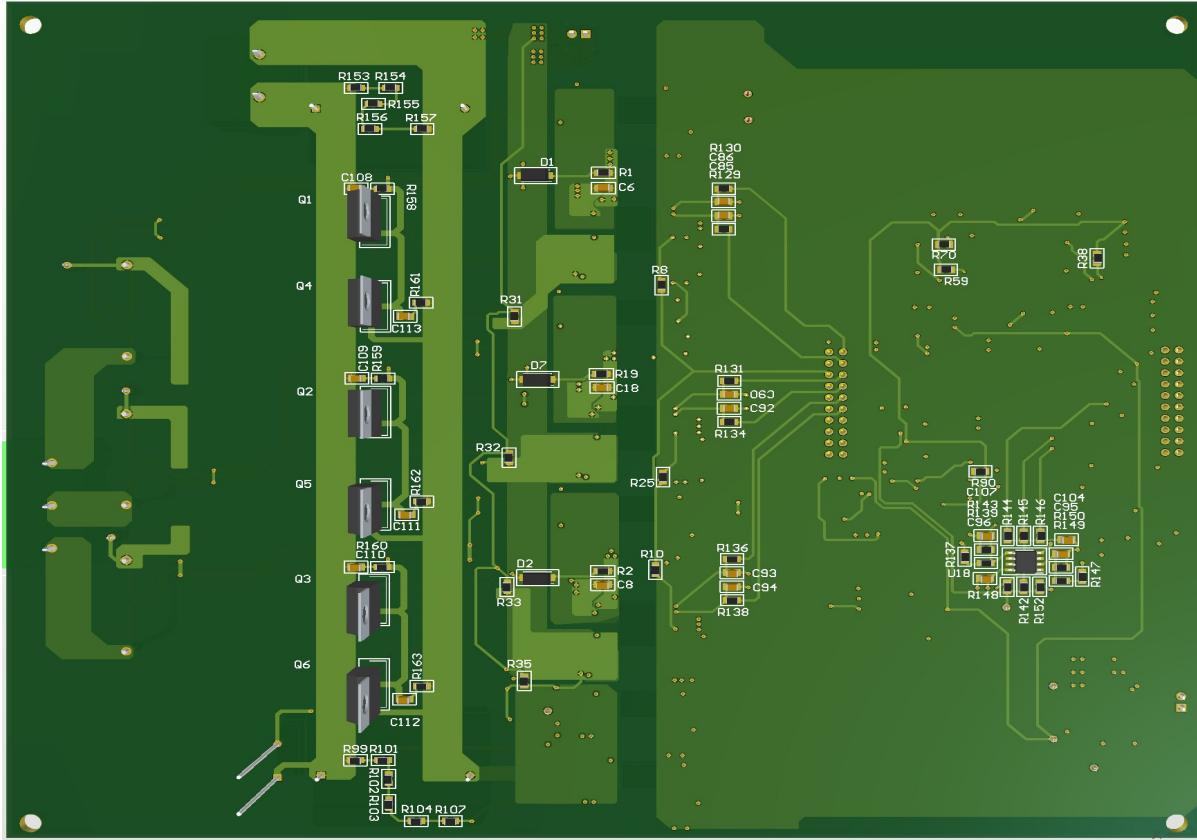

| 4.13 | Top layer component placement . . . . .                           | 50 |

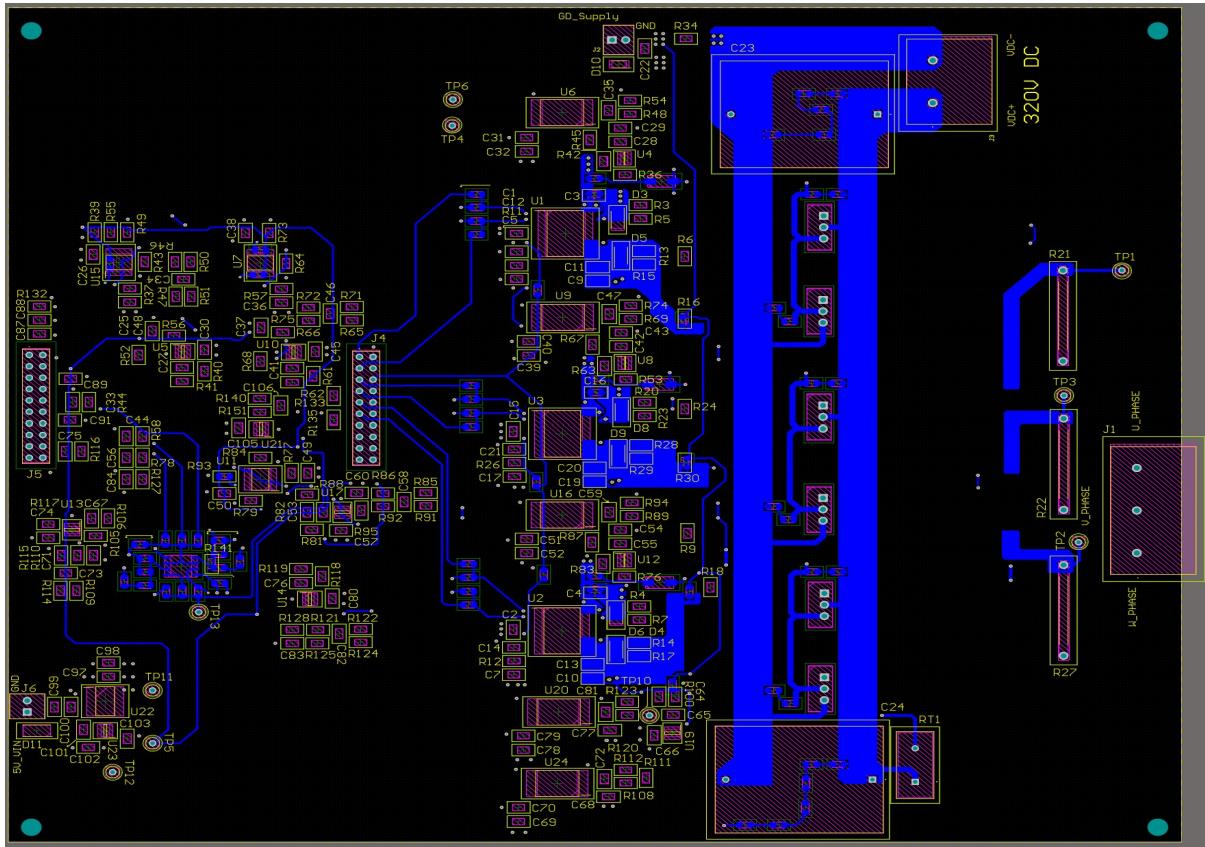

| 4.14 | Bottom layer component placement . . . . .                        | 52 |

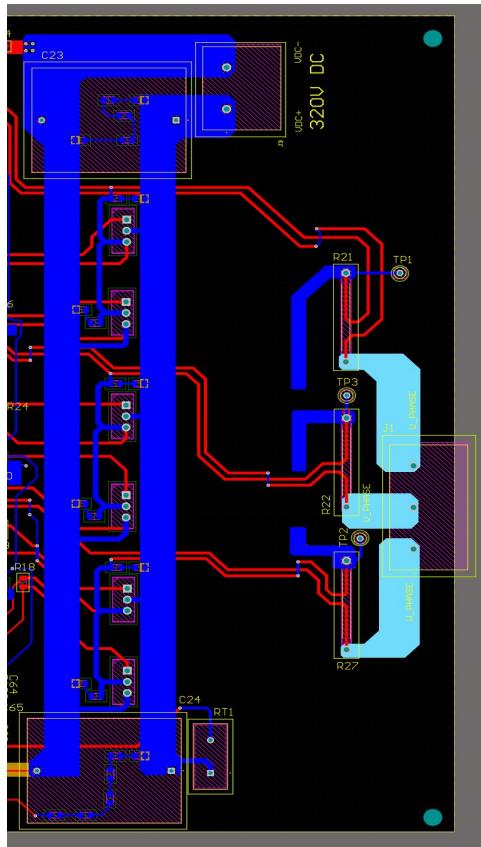

| 4.15 | Isolating power side . . . . .                                    | 53 |

| 4.16 | Isolating control side . . . . .                                  | 54 |

| 4.17 | Final PCB Top side . . . . .                                      | 55 |

| 4.18 | Final PCB Bottom side . . . . .                                   | 56 |

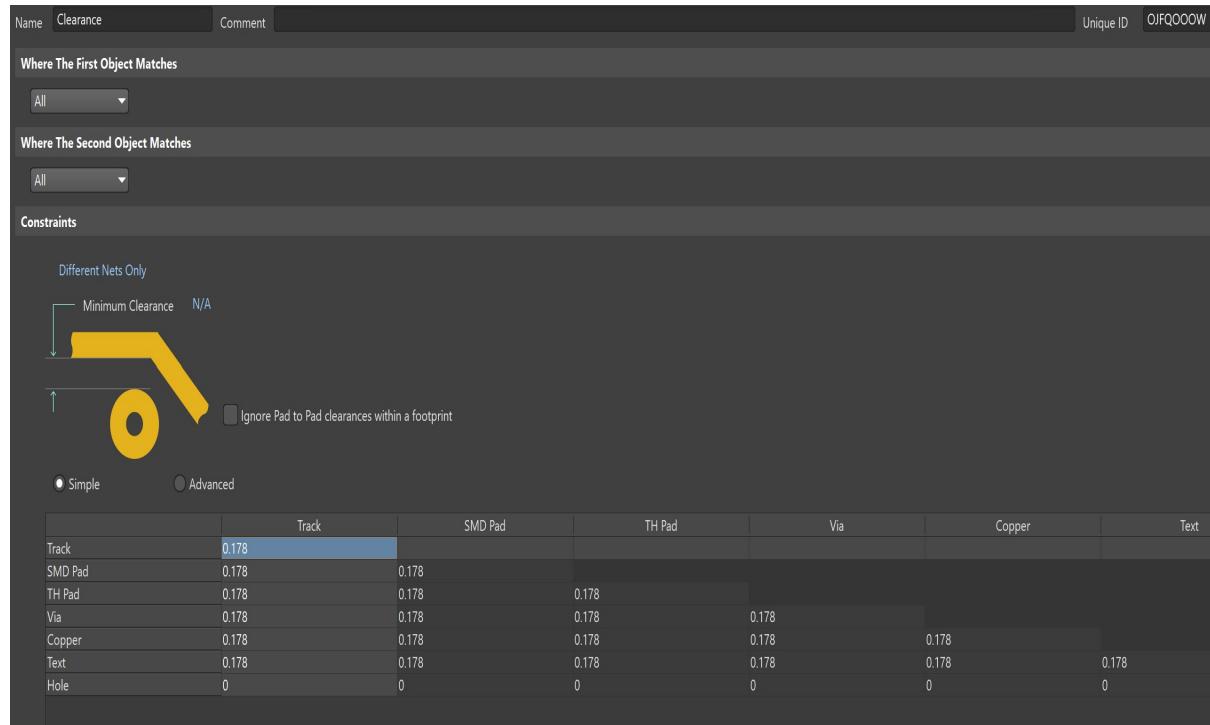

| 4.19 | Design rules for clearance . . . . .                              | 57 |

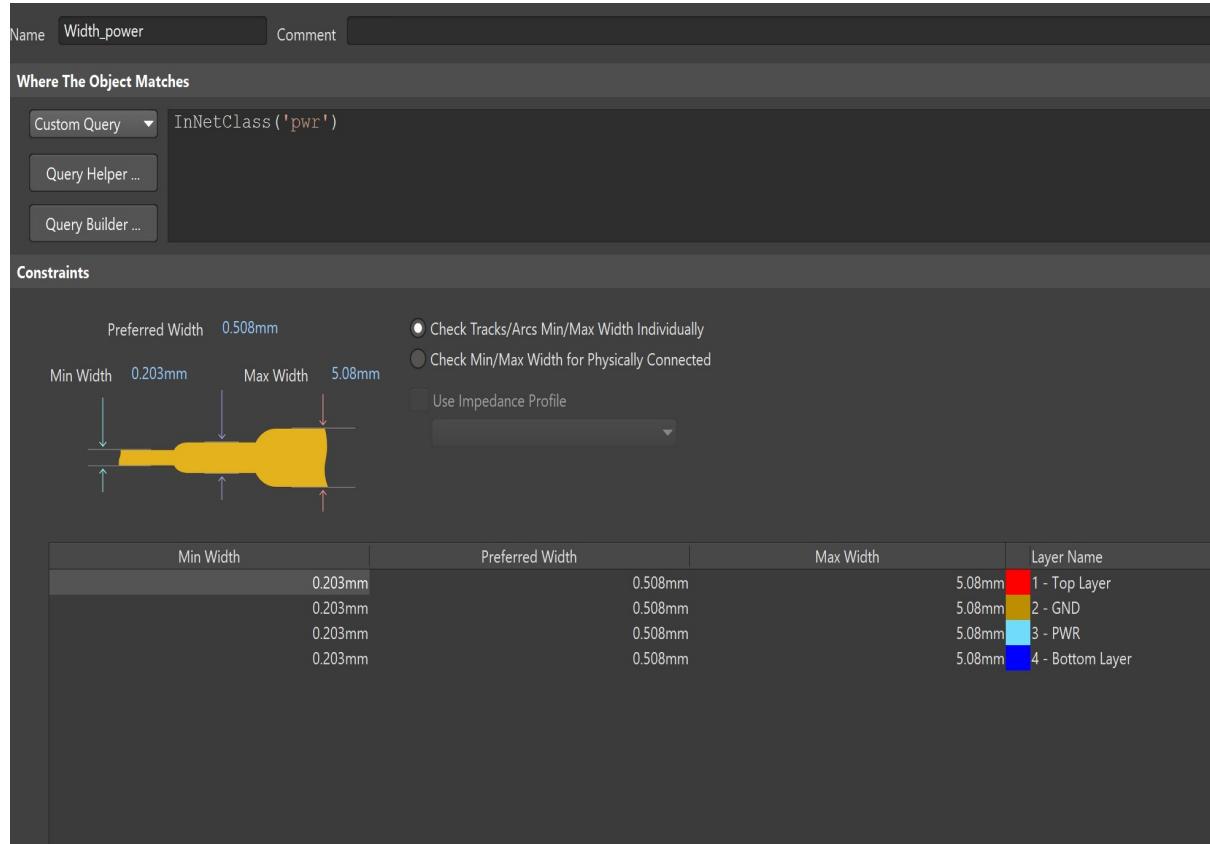

| 4.20 | Design of trace width rules . . . . .                             | 58 |

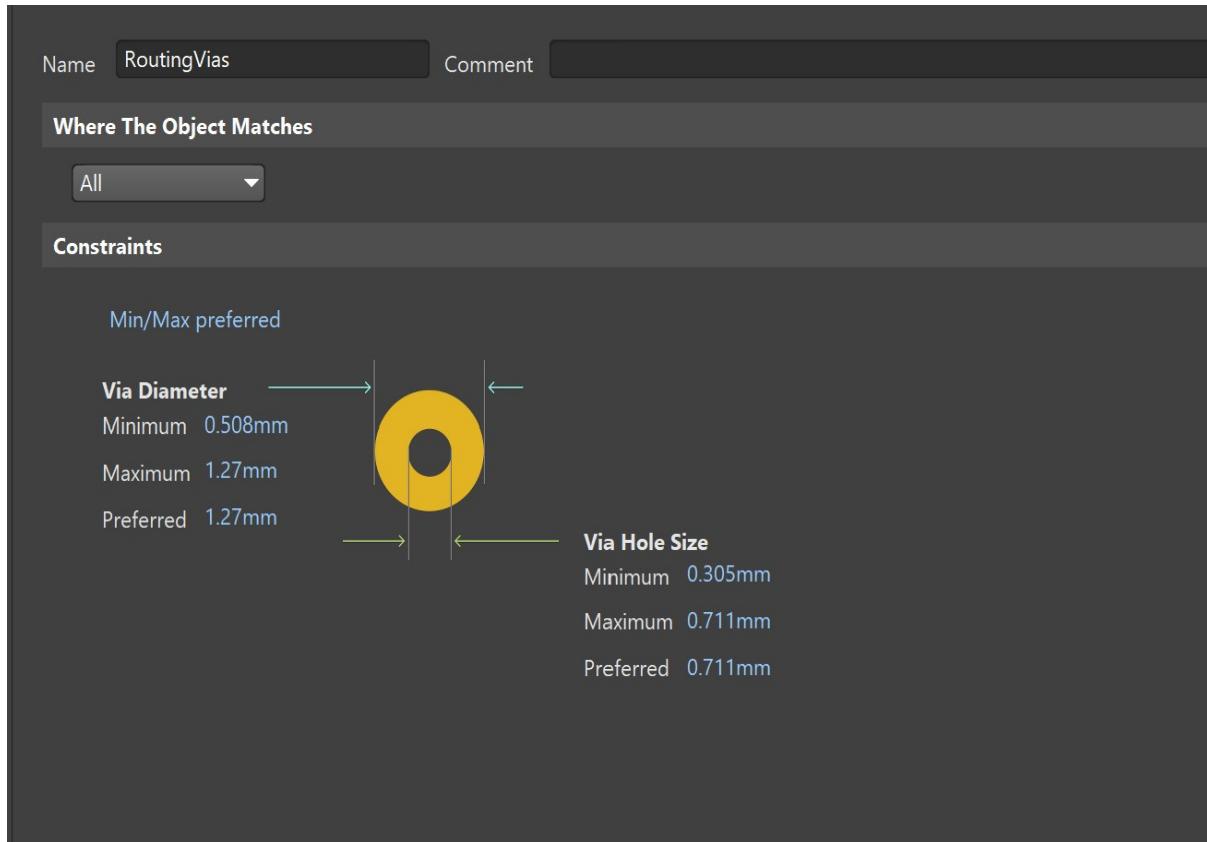

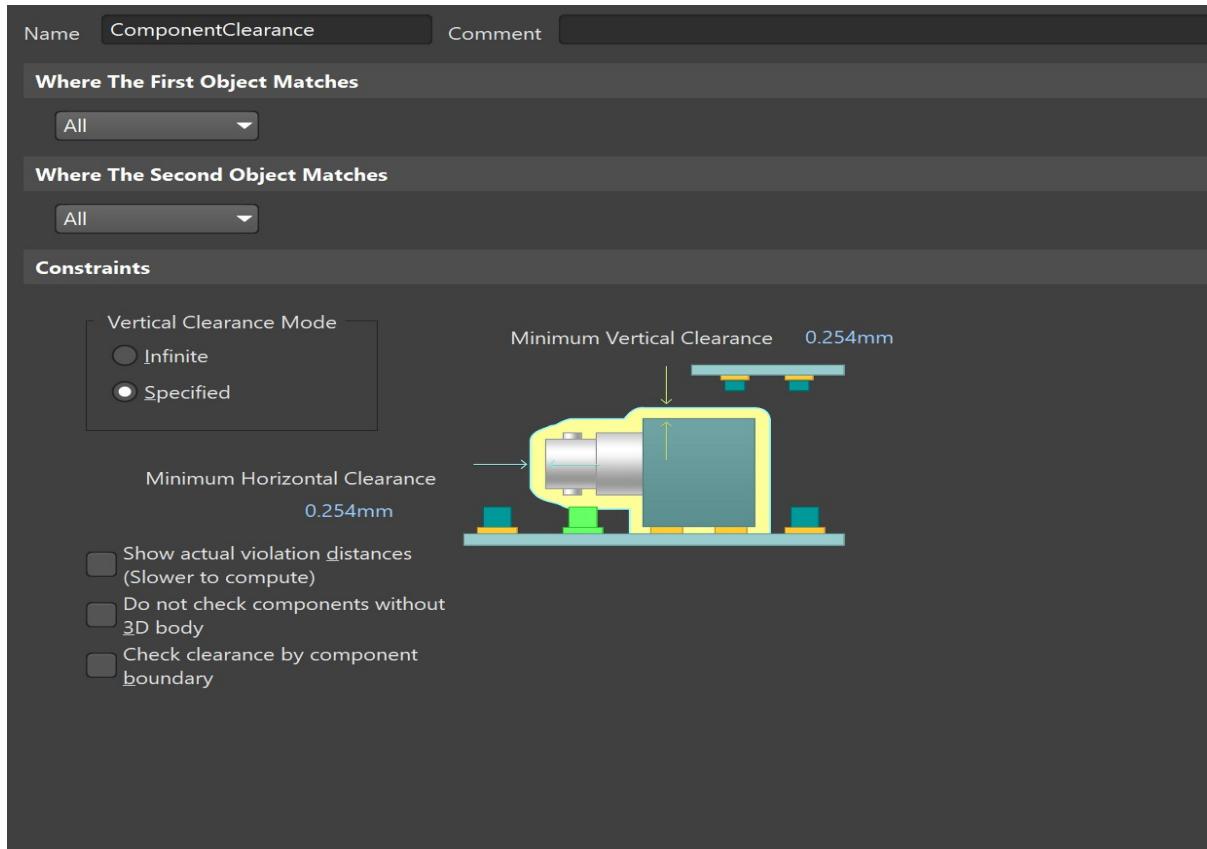

| 4.21 | Design of via design rules . . . . .                              | 59 |

| 4.22 | Design of component clearance rules . . . . .                     | 61 |

| 4.23 | Block diagram of PI Controller . . . . .                          | 62 |

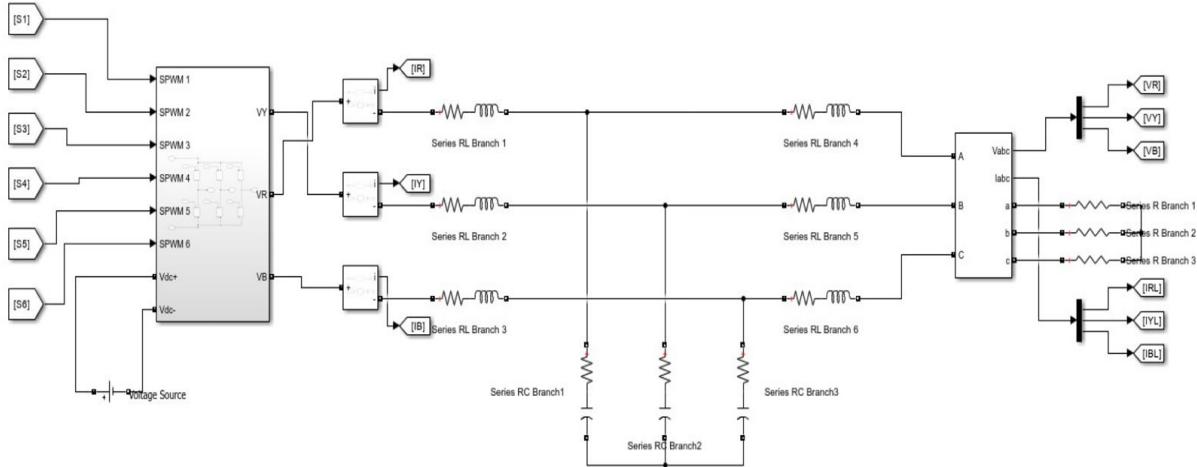

| 5.1  | Matlab simulink model of three-phase inverter . . . . .           | 66 |

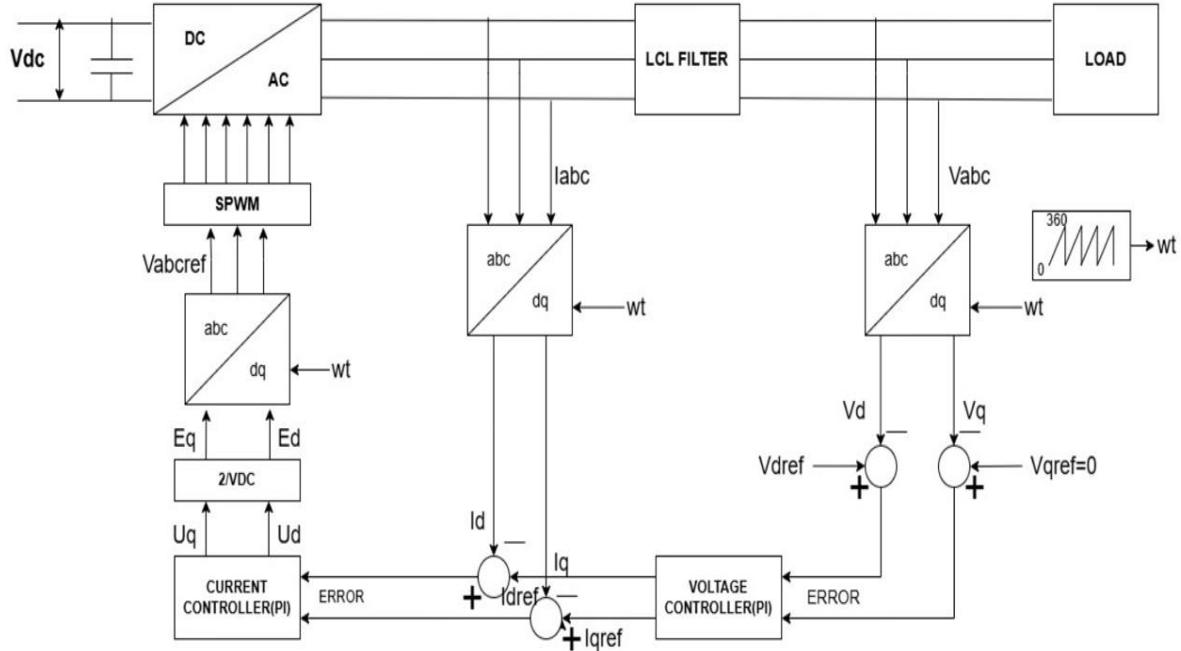

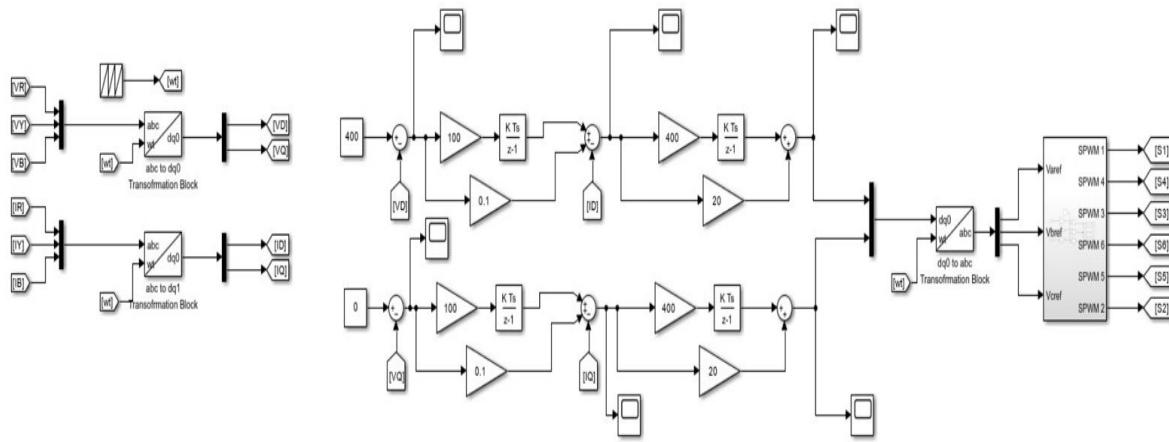

| 5.2  | Matlab simulink model of control circuit . . . . .                | 66 |

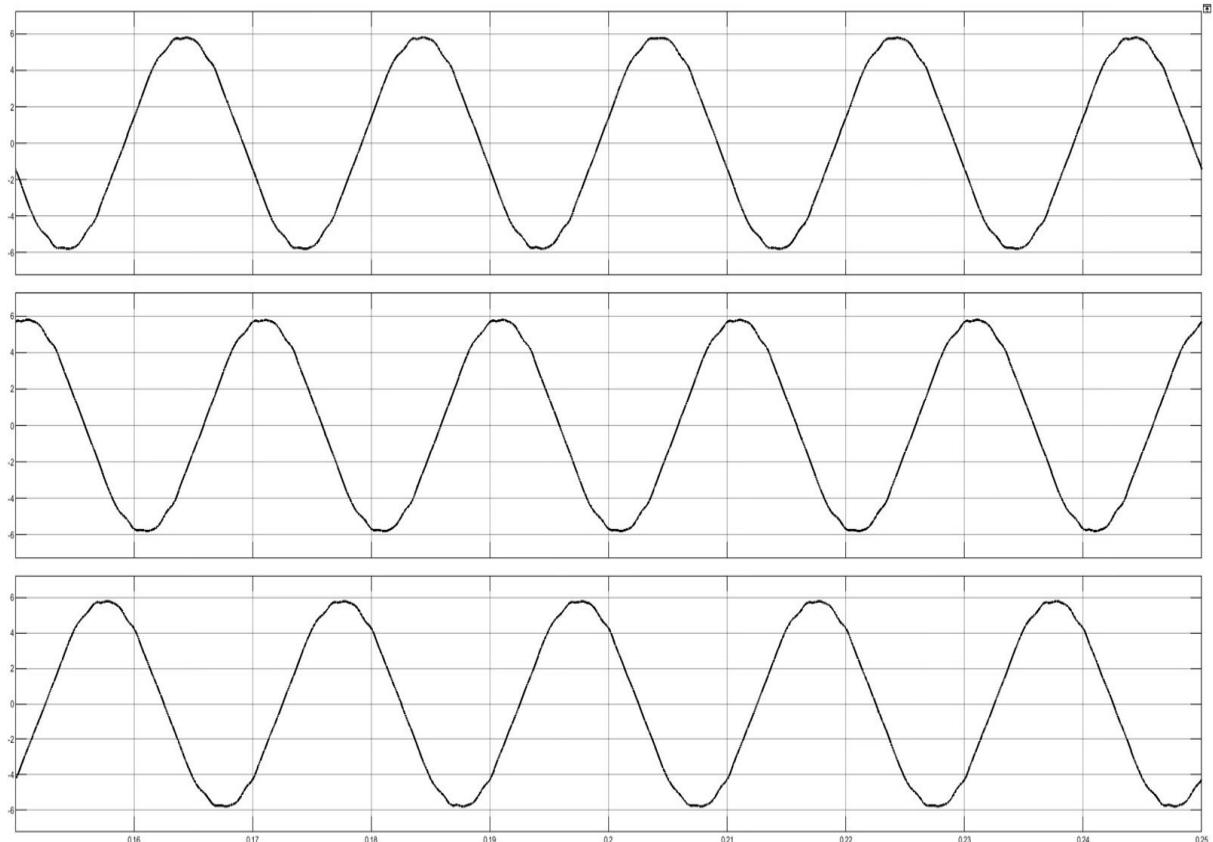

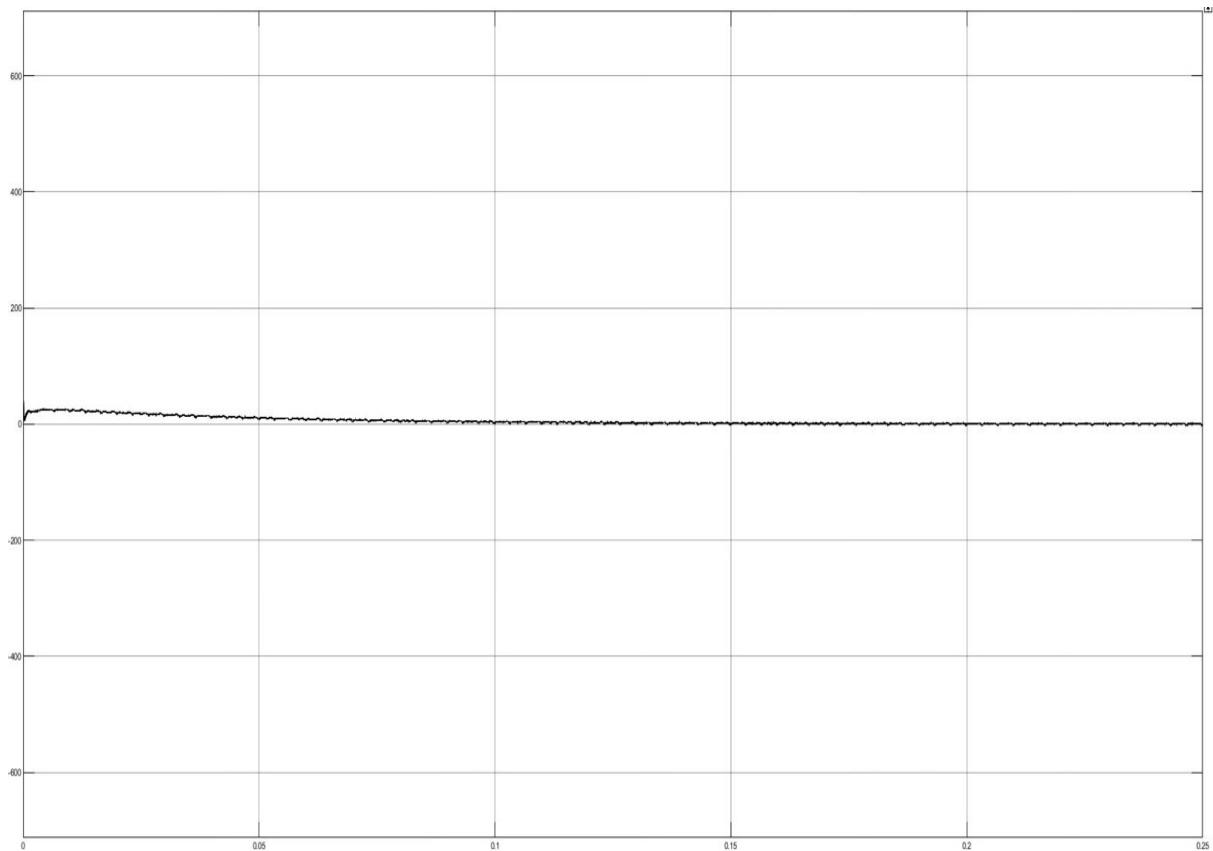

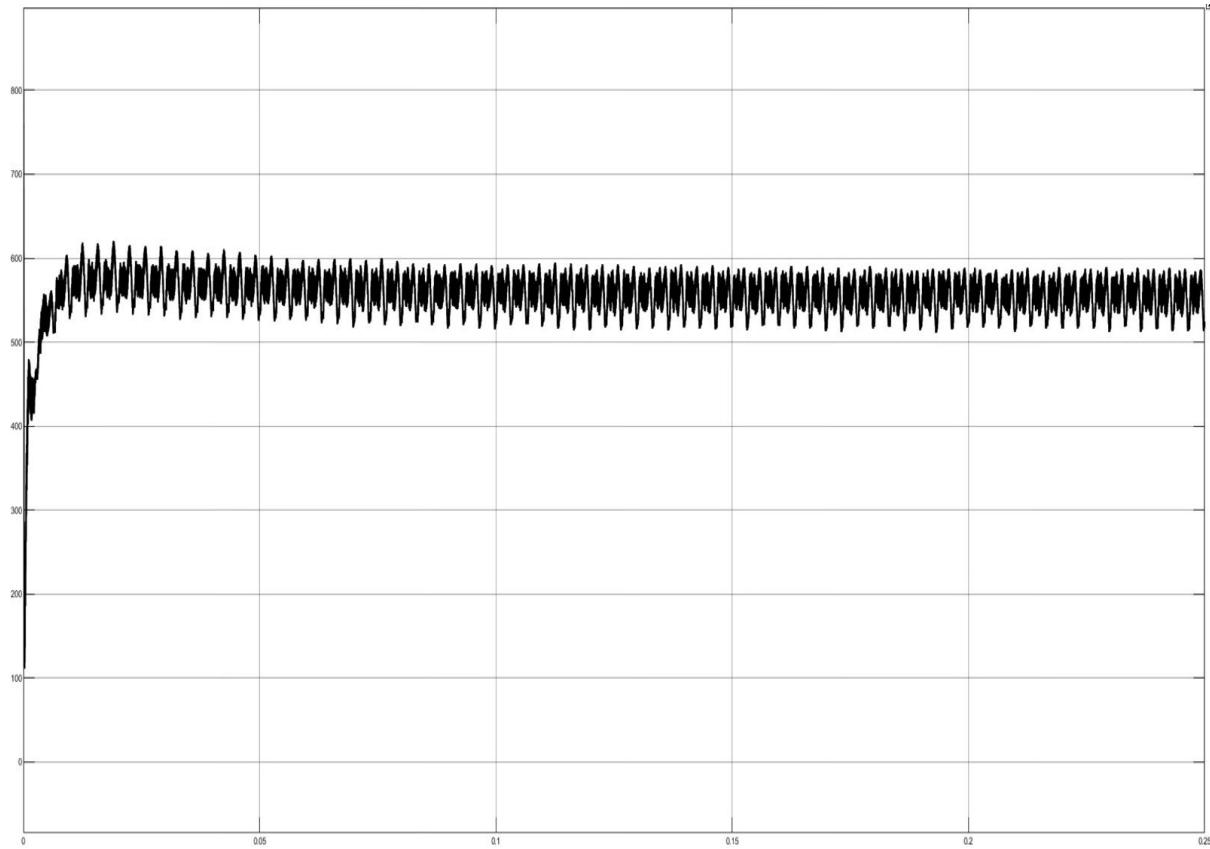

| 5.3  | The three phase output currents $I_r$ , $I_b$ and $I_y$ . . . . . | 70 |

| 5.4  | The three phase output Voltage $V_r$ , $V_b$ and $V_y$ . . . . .  | 71 |

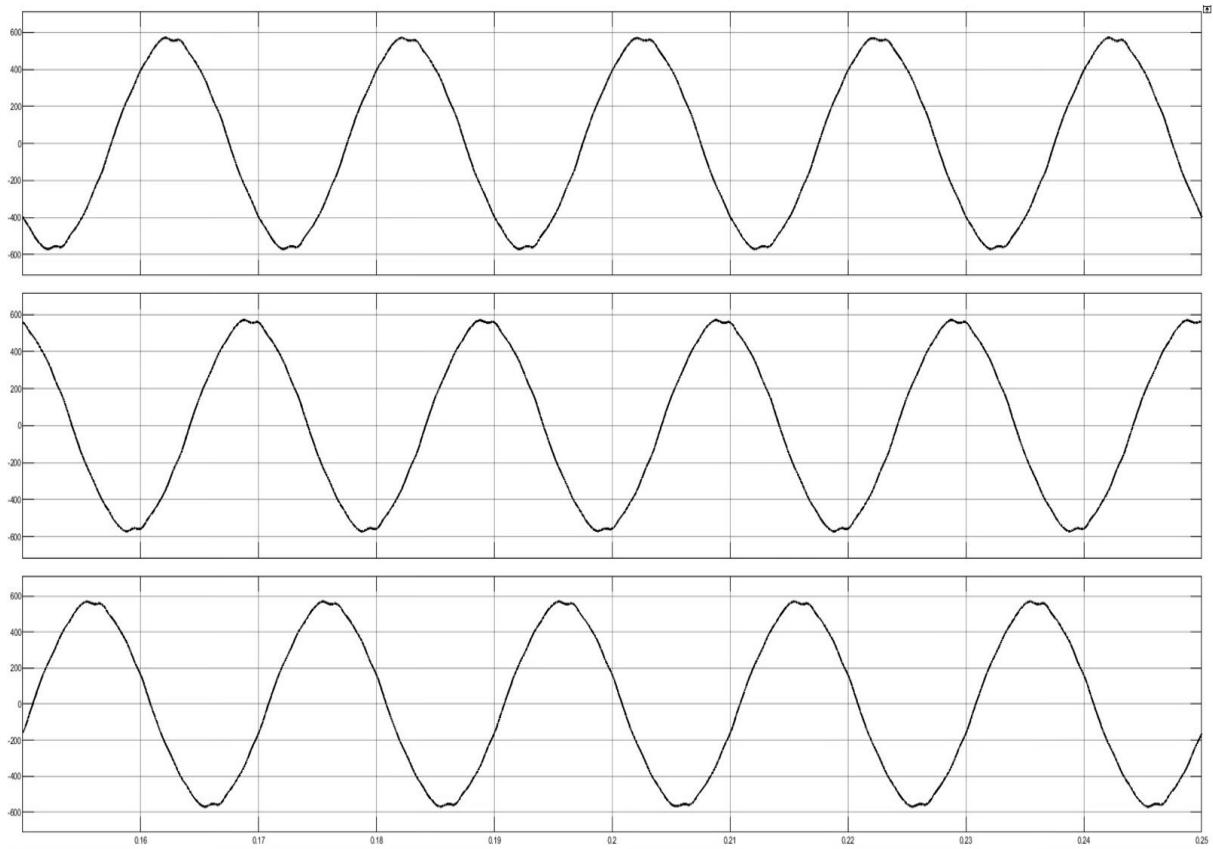

| 5.5  | The current controller PI output waveform(q-axis) . . . . .       | 72 |

| 5.6  | The voltage controller PI output waveform(q-axis) . . . . .       | 73 |

|      |                                                                |    |

|------|----------------------------------------------------------------|----|

| 5.7  | The voltage controller PI output waveform (d-axis) . . . . .   | 73 |

| 5.8  | The current controller PI output waveform (d-axis) . . . . .   | 74 |

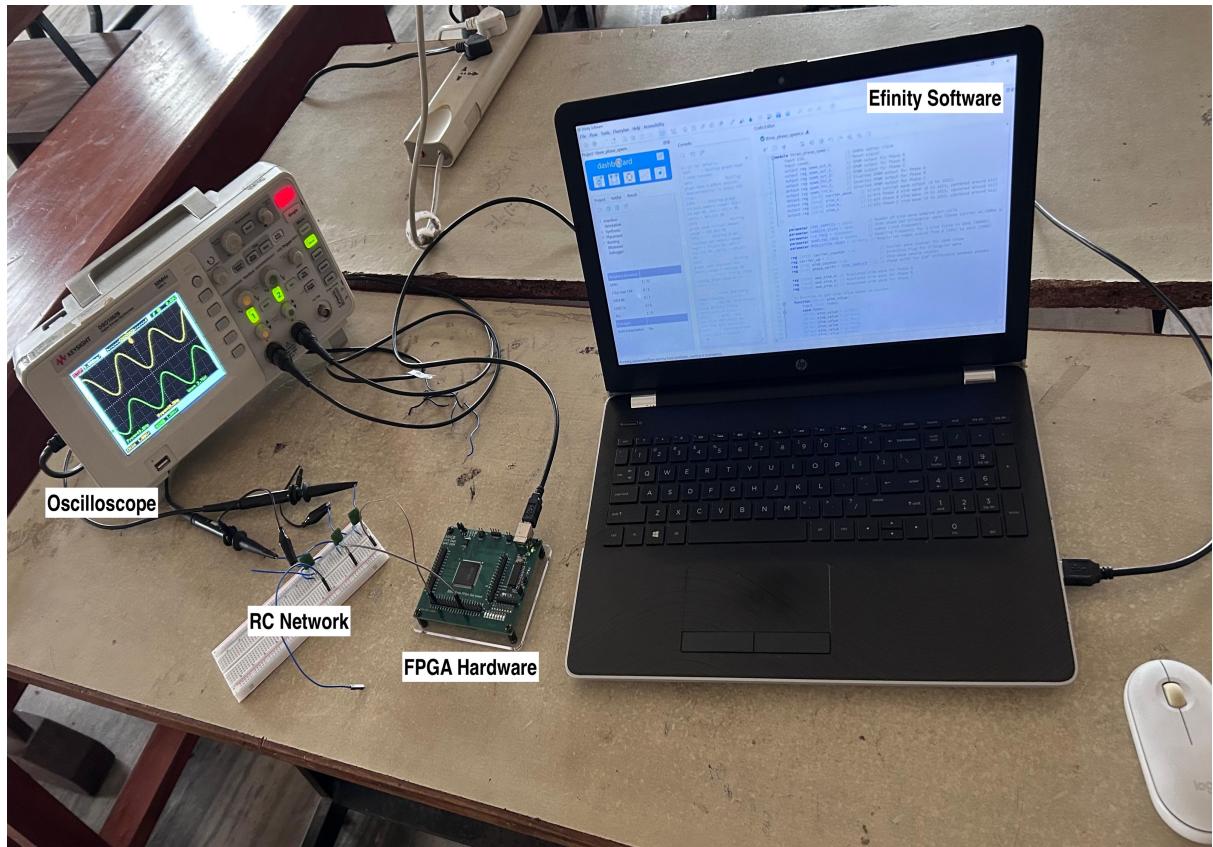

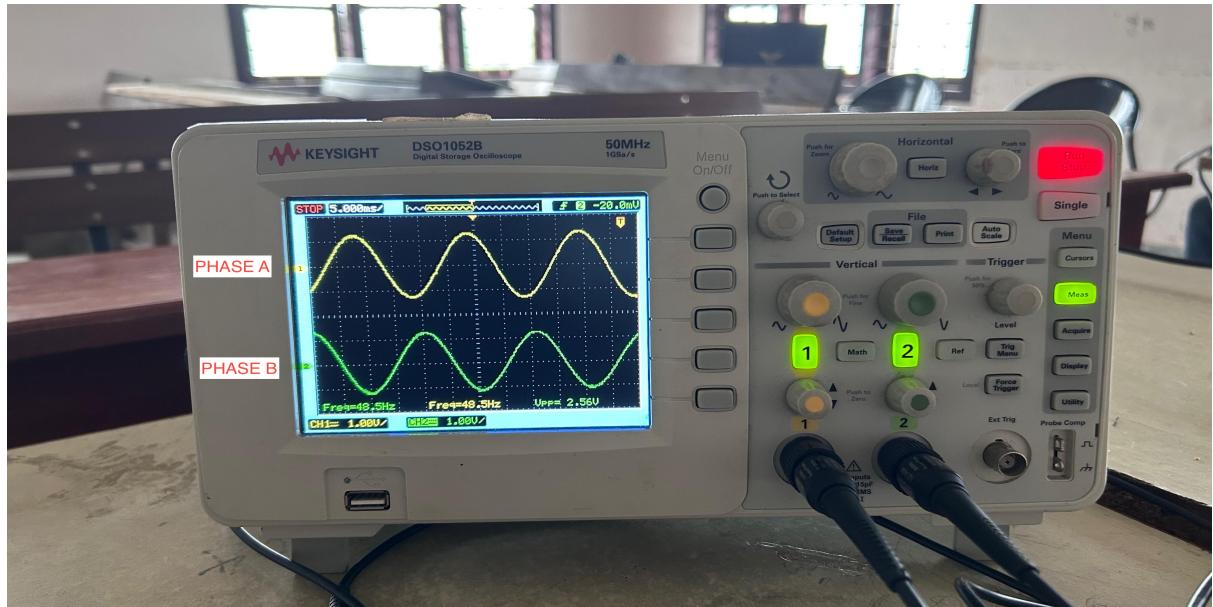

| 5.9  | Three phase hardware setup . . . . .                           | 75 |

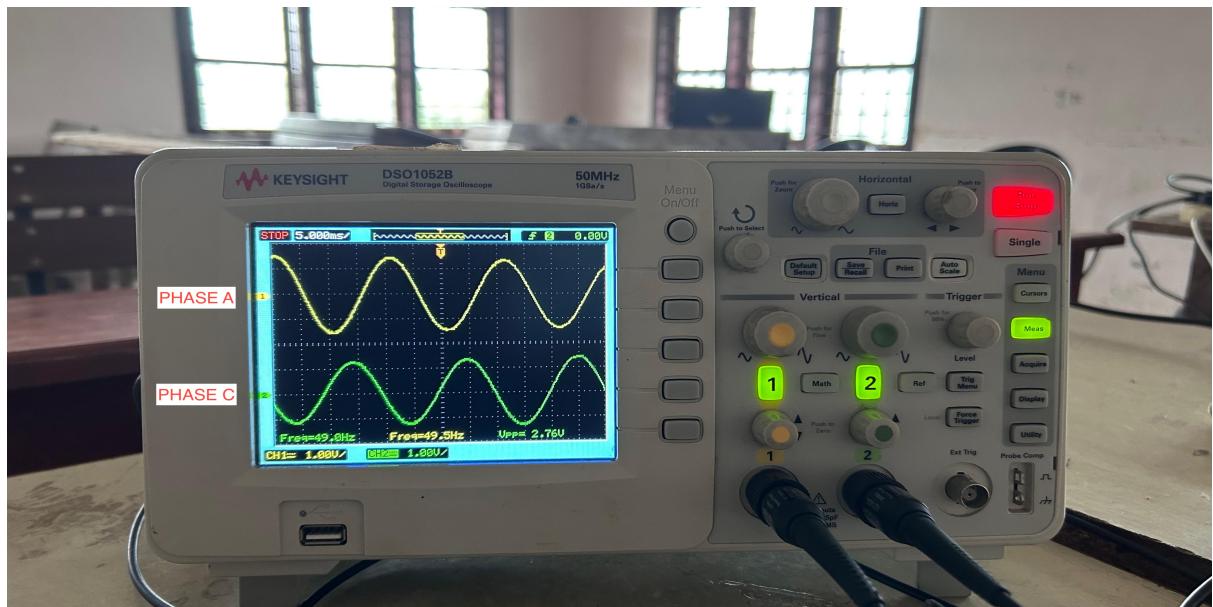

| 5.10 | Phase A and Phase B in digital oscilloscope . . . . .          | 76 |

| 5.11 | Phase A and Phase C obtained in digital oscilloscope . . . . . | 76 |

# 1 INTRODUCTION

Building upon the foundational work established in Phase 1 of this dissertation, which successfully demonstrated the generation and validation of Sinusoidal Pulse Width Modulation (SPWM) signals using the T20Q144I4 FPGA, Phase 2 marks a critical transition towards the practical implementation of a complete FPGA-based inverter system. This phase is dedicated to the design and development of a printed circuit board (PCB) for a three-phase inverter with a 1kW load capacity, serving as a comprehensive platform for testing the FPGA controller card developed in the previous phase.

The shift from pure signal generation to a fully functional power electronics system introduces several engineering challenges. These include the need for effective thermal management, the mitigation of electromagnetic interference (EMI), the careful layout and routing of components, and the integration of robust protection mechanisms. Such considerations are essential to ensure reliable operation under varying load conditions and to protect both the power electronics and control circuitry from potential faults.

While Phase 1 validated SPWM signal generation using an RC low-pass filter and simulation tools such as LTSpice, MATLAB, and GTKWave, Phase 2 enables real-world testing with actual power flow and dynamic load conditions. This progression from signal validation to power validation represents a crucial step in the development of efficient and reliable AC inverter systems. The PCB design incorporates modern power semiconductor devices, isolated gate drivers, feedback sensing circuitry, protection mechanisms for fault detection and management, and interface circuits to connect with the FPGA controller card. The hardware architecture is designed for modularity and flexibility, allowing future enhancements and modifications as research advances.

In its current initial testing phase, the three-phase inverter PCB provides a platform to evaluate the performance of the FPGA controller under realistic operating conditions. Initial tests focus on verifying basic functionality, including proper power flow, successful transmission of the SPWM signal from the FPGA to the gate drivers, and the correct operation of the detection and protection circuits. This phase addresses the practical challenges of bridging the gap between theoretical control algorithms and their hardware implementation. The insights gained from the PCB design and testing process contribute valuable knowledge to the field of power electronics, particularly in the context of FPGA-based control systems for modern inverter applications.

## 2 LITERATURE REVIEW

### 2.1 Paper 1 : FPGA Implementation of Multiple Single Phase PWM Inverters with Configurable Duty Cycle and Dead Time

The survey discusses how FPGAs offer speed, flexibility, and reconfiguration compared to traditional microcontroller-based systems. This understanding is crucial in justifying the choice of FPGA for my project, particularly because of the parallel processing capabilities and high-speed operation that are vital for real-time control of inverters. The flexibility to reconfigure control algorithms in an FPGA aligns well with my project's requirements for multiple single-phase PWM inverters with configurable duty cycles and dead time.

The survey outlines the use of Sinusoidal Pulse Width Modulation (SPWM) as an effective method of controlling inverter switches while reducing harmonic distortion. Studies by Bakar et al. and Annapoorani et al. demonstrate how SPWM can be efficiently implemented on FPGAs using VHDL or Verilog, providing a strong foundation for the FPGA-based SPWM control system in my project. The literature survey strongly advocates for FPGAs as a preferred platform due to their parallel processing, reconfiguration, and high-speed operation. These features are directly relevant to my project, which involves multiple PWM inverters with configurable control strategies.

The literature survey from the base paper provides a strong foundation for my project, particularly in its focus on FPGA-based control for inverters. Key insights into SPWM implementation, reconfiguration, and real-time control have directly influenced my design choices for implementing multiple single-phase PWM inverters with configurable duty cycle and dead time. The survey justifies the use of FPGAs over traditional microcontrollers due to their superior performance in handling complex control tasks with high speed and flexibility. Using the lessons learned from previous works, we can confidently design a system that is scalable, adaptable, and capable of delivering high-quality power conversion with reduced harmonics and optimized switching.

### 2.2 Paper 2 : Implementation of FPGA-Based MSPWM Using 6-Input LUT for Reference Signal Generation

The introduction of the supporting paper highlights the growing adoption of FPGAs in inverter systems due to their flexibility, high-speed operation, and ability to handle parallel

processing. These attributes are particularly relevant to my project, which requires the ability to control multiple single-phase inverters with independent and configurable parameters such as duty cycle and dead time.

The primary contribution of the supporting paper is the discussion on the use of 6-input LUTs for the generation of the SPWM reference signal. This LUT-based approach significantly reduces the usage of resources in the FPGA, which is critical for implementing a system that controls multiple inverters while maintaining efficiency in resource allocation.

The paper presents the innovative use of 6-input LUTs to generate high-resolution SPWM reference signals with minimal resource consumption. This LUT optimization is a crucial strategy in my project, where multiple single-phase inverters are controlled, and the efficient use of FPGA resources is essential. The paper, "FPGA-Based Implementation of MSPWM Using 6-Input LUT for Reference Signal Generation" has directly contributed to the development of my project in several ways.

- **Efficient SPWM Generation Using LUTs:** The use of 6-input LUTs to generate SPWM signals with reduced resource consumption is a key contribution. By adopting this approach, my project can efficiently manage the FPGA resources while implementing configurable duty cycles and dead time for multiple inverters.

- **Real-Time and High-Speed FPGA Operation:** The high-speed operation of FPGAs, as discussed in the paper, enables real-time control of multiple inverters, ensuring precise switching and efficient power conversion in my design.

- **Resource Optimization:** The resource optimization strategies outlined in the paper are essential for handling the multiple tasks involved in controlling multiple inverters. By reducing the size of the LUTs and efficiently managing FPGA resources, my project can maintain scalability and flexibility.

- **Overcoming Implementation Challenges:** The paper addresses key challenges such as managing precision and resource trade-offs, providing solutions that my system can apply to ensure the accuracy and performance of my system without exceeding the available FPGA resources.

In summary, the literature survey in the supporting document has significantly influenced the approach of my project to SPWM generation, resource optimization, and real-time control,

all of which are critical for the successful implementation of multiple single-phase PWM inverters.

## 2.3 Paper 3 : Implementation in FPGA of an Alternative Modulation Strategy for Energy Balancing Purposes

The supporting article highlights the increasing role of FPGA-based control systems in inverter applications, particularly in high-power, grid-connected, and renewable energy systems. These applications demand real-time control, flexibility, and energy balancing, making FPGAs the ideal platform for implementing advanced modulation strategies. The paper underscores the importance of using FPGAs to optimize switching patterns for efficient energy distribution, which is also a core aspect of my project. The paper discusses multiple PWM techniques, including phase-shift PWM (PS-PWM) and level-shift PWM (LS-PWM), which are particularly useful in multilevel inverters. However, these PWM techniques also offer insight into the management of power distribution and harmonic distortion, which are critical in my single-phase PWM inverter project.

The core focus of the supporting paper is the implementation of an alternative modulation strategy based on FPGAs aimed at energy balance in multilevel inverters. The paper demonstrates how FPGAs are used to manage complex switching algorithms and energy balancing through advanced modulation strategies. This is directly applicable to my project, where managing configurable duty cycles and dead time involves complex real-time adjustments that FPGAs are well suited to handle.

The paper emphasizes the need for energy balancing in multilevel inverters to ensure reliable operation, reduce system losses, and extend the lifetime of inverter components. The supporting paper provides a detailed comparison of harmonic distortion in various PWM techniques, which is critical in ensuring high power quality in grid-connected inverter systems. In my project, ensuring low THD and high power quality is essential, especially when controlling multiple inverters simultaneously.

The supporting document highlights the advantages of using FPGAs to implement advanced modulation strategies in inverter control systems, particularly for energy balance and harmonic performance. These insights are directly relevant to my project, where FPGAs enable flexible and high-speed control over multiple inverters with configurable duty cycles and dead time.

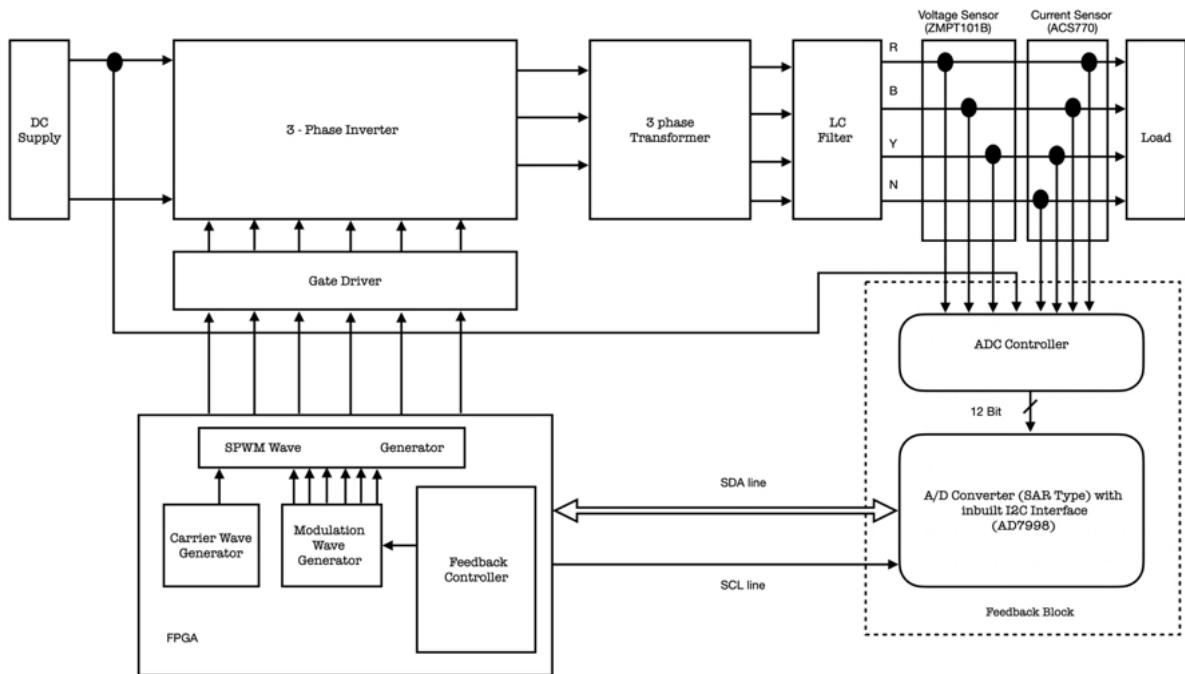

### 3 METHODOLOGY

The development of a 1kW three-phase inverter with multifrequency capability marks a notable step forward in the versatility of power electronics. This system finds applications in industrial motor drives, aerospace power systems, and frequency conversion equipment. My design brings together several carefully engineered power processing stages to deliver reliable three-phase AC output at user-selectable frequencies of 50Hz and 60Hz. The approach I have taken includes DC-AC conversion, step-up voltage transformation, and robust protection mechanisms that meet industrial standards. My system operates from a regulated 320V DC

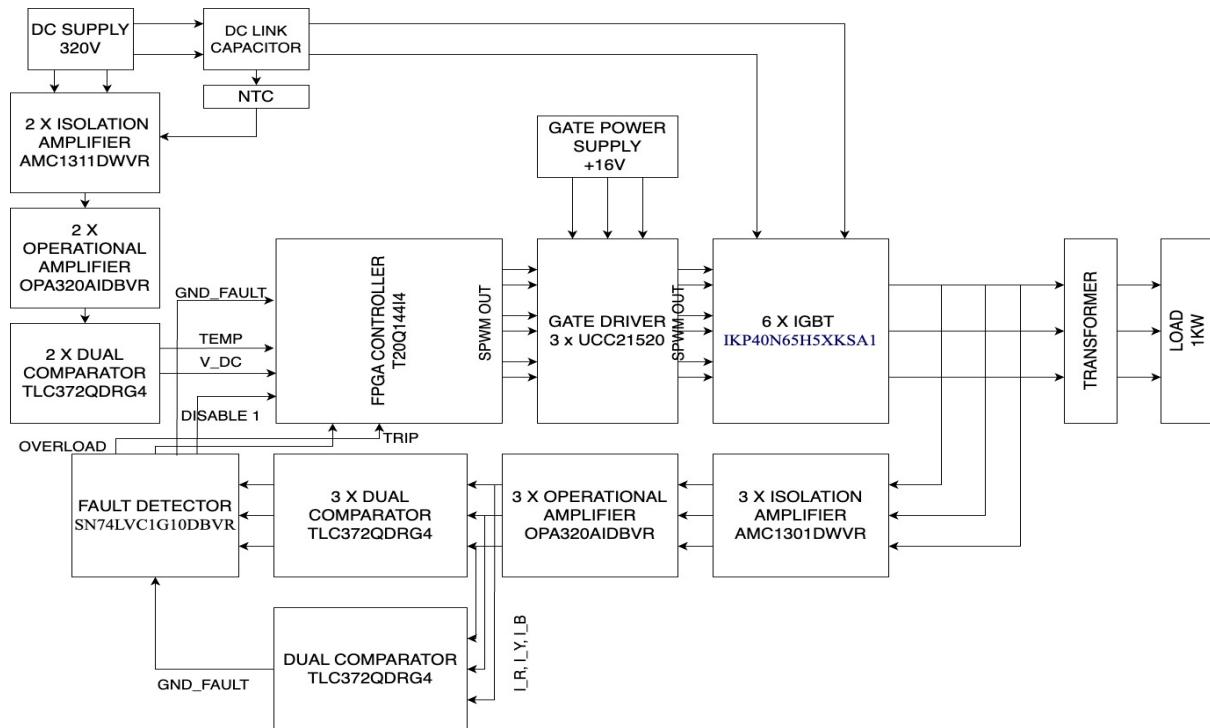

Figure 3.1: The Proposed System

bus that serves as the primary power source. This DC input undergoes conversion through a six-switch IGBT-based three-phase bridge using Infineon IKP40N65H5XKSA1 power transistors rated at 650V/40A. I specifically selected these components for their generous  $4.16\times$  peak current margin and  $2\times$  voltage headroom, which helps ensure dependable operation even when load conditions vary. These IGBTs switch at 20kHz to generate three-phase AC waveforms on the primary side with minimal distortion. For gate drive signals, I have implemented isolated TI UCC21520DW drivers that provide 5kVRMS isolation and 150V / ns common mode transient immunity - features I found essential for rejecting noise in environments with rapid voltage transitions. The generated AC signals pass through the EE-55 transformer. The EE-55

Figure 3.2: The Proposed Inverter Design

transformer handles the voltage conversion from 101.8V to 400V. I chose the EE-55 core configuration after careful consideration of several factors, including power handling capability, core loss characteristics, and manufacturing practicality. The EE core structure offers a good balance between winding ease and magnetic efficiency, with the added benefit of being more readily available and cost-effective than specialized core types.

For system protection, I have implemented a multilayered approach that combines basic and advanced safety mechanisms. This strategy ensures long-term reliability and rapid response to fault conditions. The thermal management system I designed uses appropriately sized heatsinks. Temperature monitoring is handled by strategically placed NTC thermistors that continuously check operating temperatures, ensuring that they remain well below the 175 °C maximum rating of the IKP40N65H5XKSA1 IGBTs even under full load.

I paid particular attention to electromagnetic compatibility in this design. The 4-layer PCB implementation features dedicated ground and power planes that significantly reduce loop inductance and common-mode emissions. The EE-55 transformers, while not offering quite the same inherent EMI advantages as toroidal types, are complemented by carefully designed filtering components to maintain CISPR 22 Class A compliance. The FPGA-based control system that I developed provides precise timing for dead-time insertion, frequency selection between 50Hz and 60Hz, and coordinated response to fault conditions.

My methodology delivers a robust platform for frequency-flexible power conversion while meeting industrial standards, including IEC 61800-5-1 and IEC 60664-1. The three independent EE-55 transformers enhance phase balance and isolation, which I found crucial to delivering high-quality three-phase power. The combination of IKP40N65H5XKSA1 IGBT and UCC21520DW gate drivers ensures excellent switching performance at 20kHz, with sufficient headroom for reliable operation under various thermal and electrical stress conditions. The EE-55 transformer configuration adapts well to multiple frequencies, and when paired with the protection mechanisms and thermal management systems I have implemented, ensures dependable operation across diverse environmental conditions and load profiles.

Through extensive testing and refinement, I have created a system that balances performance, reliability, and cost-effectiveness for applications that require precise frequency control and stable three-phase output power.

## 4 DESIGN ASPECTS

The design and implementation of a three-phase Voltage Source Inverter (VSI) using EE55 transformers encompass multiple critical stages. Each phase of the process is integral to achieving a robust, efficient, and reliable system capable of meeting the demands of various applications. Below is an exploration of the key design aspects as detailed in the project.

1. Topology Selection : The first step in designing the three-phase VSI involves selecting the appropriate topology. This decision is influenced by several factors, such as the required power rating, efficiency considerations, and the specific application for which the inverter is intended. For this 1kW design, a three-phase bridge topology with EE55 ferrite transformers was selected. Based on the search results, the EE55 transformers can handle between 1000W-1500W of power, making them suitable for this application. The EE55 core structure offers excellent power handling capability while maintaining reasonable size constraints. This topology supports operation at 50Hz and 60Hz frequencies, providing versatility for various regional power standards while maintaining good efficiency levels.

2. Component Selection : Once the topology is finalized, the next step focuses on the careful selection of electronic power components. The reliability and efficiency of the VSI depend heavily on the components used in its construction. For this design, Infineon IKP40N65H5XKSA1 IGBTs were selected for their superior switching characteristics, featuring 650V breakthrough voltage with a factor of 2.5 lower gate charge and factor 2 reduction in switching losses compared to previous generations. These IGBTs are optimized for switching frequencies from 30kHz to 100kHz, making them ideal for 20kHz operation in this inverter. The gate driver selection was centered on the UCC21520DW, which provides a 4A source and 6A sink peak current with reinforced isolation of 5.7kVRMS and a minimum of 125V/ns common-mode transient immunity. For the transformers, EE55 ferrite cores were chosen based on their working frequency range of 20kHz-500kHz and output power capability of 80-2000W, as indicated in the search results. EE55 transformers offer convenient winding characteristics, moderate pricing, and high reliability according to manufacturer specifications.

3. Circuit design : The design phase progresses with the creation of the circuit architecture for the VSI. This involves a detailed schematic design that incorporates key elements such as the configuration of the three-phase bridge with EE55 transformers. According to the search results, the EE55 transformers have a horizontal structure with dimensions of approximately 57.3mm×54.5mm×51.0mm, allowing for efficient PCB layout. The transformers can operate

at the required 20kHz switching frequency and handle the 1kW power requirement. Circuit protection includes both basic mechanisms (fuses with 10-20ms response time) and advanced features (desaturation detection with <1us response time). The layout incorporates a 4-layer PCB design with dedicated ground and power planes to minimize loop inductance and reduce common-mode emissions. The EE55 transformers, with their 16-20 pin configuration, as mentioned in the search results, provide sufficient connection points for complex winding arrangements needed in three-phase applications.

4. Central Controller Board : The design also includes the development of the Central Controller Board, which serves as the brain of the VSI. An FPGA-based control system is utilized as the central processing unit, providing precise timing for dead-time insertion, frequency selection (50Hz/60Hz), and synchronous response to fault conditions. The controller board emphasizes seamless integration with other components, including IGBTs IKP40N65H5XKSA1, UCC21520DW gate drivers, and sensing circuits. The UCC21520 gate drivers feature internal functional isolation between the two secondary-side drivers, allowing a working voltage of up to 1500VDC. Each driver can be configured for half-bridge operation with programmable dead-time, ensuring precise control over the switching sequences. A disable pin allows for emergency shutdown of both outputs simultaneously, with fail-safe measures forcing both outputs low in case of primary-side logic failures.

5. Control Algorithms: A critical aspect of the design is the development of control algorithms that dictate the operation of the inverter. These algorithms are designed to achieve specific performance objectives, such as maintaining voltage regulation, minimizing harmonic distortion, and ensuring fault tolerance. For the three-phase VSI, synchronously rotating reference frame control was implemented for its simplicity and effectiveness in grid-connected applications. The control system generates precise PWM signals at 20kHz with <100ns dead time to minimize distortion. Temperature monitoring via NTC thermistors maintains junction temperatures below the IKP40N65H5XKSA1 maximum rating of 175 ° C even under maximum load conditions. The FPGA implementation allows for adaptive control strategies that can respond to changing load conditions or adjust parameters based on the selected operating frequency (50Hz/60Hz), ensuring optimal performance across the full operating range. The operating temperature range of the EE55 transformers from -40 ° C to +125 ° C (as indicated in the search results) provides sufficient thermal headroom for reliable operation.

6. Testing and Optimization : After the design and implementation are completed, the

system undergoes rigorous testing and optimization. This phase ensures that the VSI meets the desired specifications and performs reliably under various operating conditions. Testing involves evaluating the system at different frequencies (50Hz and 60Hz) and load conditions to verify performance meets the efficiency targets. According to the search results, the EE55 transformers can operate efficiently within the  $-40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$  temperature range, which is verified during thermal testing. Parameters such as total harmonic distortion, EMI compliance, and thermal behavior are analyzed. Special attention is given to the transformer's performance at the 20kHz switching frequency, as the search results indicate that this is within the EE55's optimal working frequency range of 20kHz-500kHz. The testing confirms that the EE55 transformers can handle the required power levels of 1000W as specified in the search results for models like the 55EE-1111BNL, which is rated for 400VAC, 1000W output with 12VDC input at 100kHz.

The design of a three-phase VSI using EE55 transformers, IKP40N65H5XKSA1 IGBTs, and UCC21520DW gate drivers represents a comprehensive integration of advanced components for superior performance. The EE55 transformer configuration provides excellent power handling capability and frequency response, while the selected IGBTs and gate drivers ensure efficient switching performance optimized for 20kHz operation. By meticulously addressing these aspects, the design achieves good efficiency, EMI performance, and thermal management, making it suitable for a wide range of applications that require multi-frequency capability and high reliability.

#### 4.1 Sinusoidal Pulse Width Modulation (SPWM)

Sinusoidal Pulse Width Modulation (SPWM) is a widely used technique in power electronics to convert DC power to an AC output with a sinusoidal waveform. This method is fundamental in inverters used for applications such as motor drives, renewable energy systems, and uninterruptible power supplies (UPS). By modulating the width of the pulses in a way that corresponds to a sine wave, SPWM ensures the generation of an AC output with reduced harmonic distortion and precise voltage regulation. Two common SPWM techniques, unipolar SPWM and bipolar SPWM, offer distinct advantages and trade-offs, making the selection process application specific.

#### 4.1.1 Unipolar SPWM

Unipolar SPWM generates the output waveform by comparing a sinusoidal reference signal with two carrier signals that are  $180^{\circ}$  out of phase. This results in the output voltage switching between 0 and  $+V_{dc}$  or 0 and  $-V_{dc}$ , avoiding direct transitions between  $+V_{dc}$  and  $-V_{dc}$ . The staggered nature of the voltage transitions makes unipolar SPWM efficient and reduces harmonic distortion.

##### Advantages of Unipolar SPWM:

- **Lower Harmonic Distortion:** Dominant harmonics appear at twice the carrier frequency, making it easier to filter out unwanted components.

- **Reduced Electromagnetic Interference (EMI):** Smaller voltage transitions and reduced high-frequency content minimize EMI.

- **Lower Switching Losses:** Fewer and less frequent transitions between high voltage levels reduce power loss.

Despite these benefits, unipolar SPWM has a significant limitation: lower DC bus utilization. This means that the amplitude of the fundamental output voltage is reduced in comparison to the available DC voltage, making it unsuitable for applications that require the maximum output voltage.

#### 4.1.2 Bipolar SPWM

Bipolar SPWM, on the other hand, compares a single sinusoidal reference signal with a single carrier signal. The output voltage switches directly between  $+V_{dc}$  and  $-V_{dc}$ , simplifying the implementation and ensuring better utilization of the DC bus.

- **Higher DC Bus Utilization:** Bipolar SPWM delivers a higher output voltage amplitude, maximizing the available DC input voltage.

- **Simpler Implementation:** The use of a single carrier signal and a straightforward comparison simplifies circuit design.

- **Robust Performance:** Bipolar SPWM is less affected by load imbalances and can maintain stable operation under varying conditions.

However, the higher voltage swings in bipolar SPWM result in increased switching losses and slightly higher harmonic distortion. These challenges can be addressed by employing efficient semiconductor devices (e.g., MOSFETs) and using filtering techniques such as RC or LC networks.

For this dissertation, bipolar SPWM was selected as the preferred modulation technique due to its superior DC bus utilization and straightforward implementation. These characteristics make it highly suitable for applications that require robust and high-quality power conversion. The following factors influenced this choice:

- **Higher Output Voltage:** Bipolar SPWM ensures the fundamental output voltage amplitude is closer to the DC input, which is essential for driving inductive loads such as motors.

- **Simpler Control:** The simpler logic of bipolar SPWM aligns well with FPGA-based implementations, minimizing resource utilization while achieving reliable performance.

- **Robust Operation Under Load Variations:** Bipolar SPWM demonstrates consistent performance even under unbalanced load conditions, which aligns with the project's focus on ensuring stability and efficiency.

## 4.2 H-Bridge Topology in SPWM Inverter Systems

The H-Bridge is a fundamental building block of inverter systems, especially in DC-AC converters. The H-Bridge circuit consists of four switches (transistors, MOSFETs, or IGBTs) arranged in an H-like configuration. By controlling which switches are turned on and off, the current direction across the load can be controlled, allowing for the generation of an AC waveform. In the H-Bridge, switching the diagonal pairs of switches on and off generates positive and negative voltage across the load, producing the necessary AC output. This architecture is crucial to achieve high efficiency in inverters. For three-phase inverter systems, multiple H-Bridge configurations are used to generate the three AC phases, each shifted by 120 degrees. The simplicity of the H-Bridge design makes it a highly reliable and widely adopted method for motor control and inverter applications.

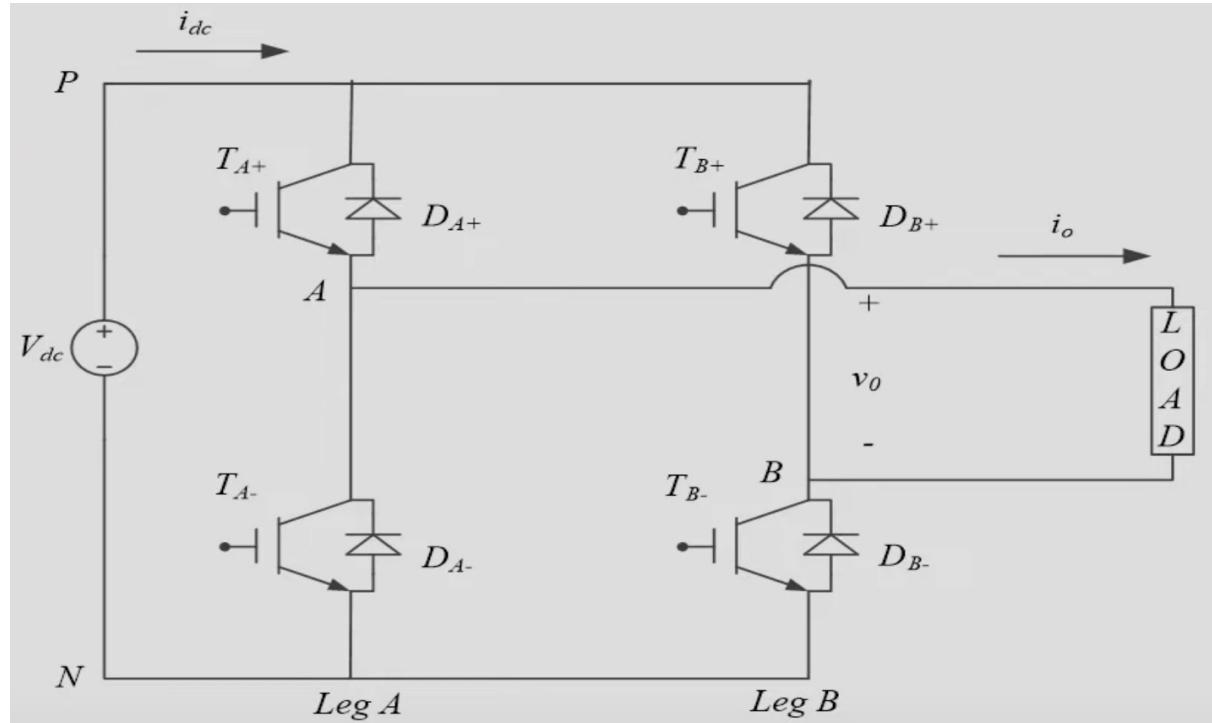

The H bridge converter is a popular and versatile converter used in various applications. It consists of four IGBTs and four antiparallel diodes, with Ta+ and Tb- being the upper and

Figure 4.1: H - Bridge Topology

lower diodes, respectively. The DC bus is denoted by P and N, and the load is connected between these nodes. The voltage between A and B is denoted by  $v_o$ , and the load current is denoted by  $i_o$ . The H bridge converter can be divided into four possible switching combinations:  $T_{A+}$  and  $T_{B-}$  are on together,  $T_{A+}$  and  $T_{B+}$  are diagonal switches,  $T_{A+}$  and  $T_{B-}$  are diagonal switches,  $T_{A+}$  and  $T_{B+}$  are diagonal switches,  $T_{A+}$  and  $T_{B+}$  are upper or lower switches, and  $T_{A+}$  and  $T_{B+}$  are both upper switches and  $T_{A+}$  and  $T_{B-}$  together.

To analyze each switching combination and their corresponding equivalent circuit, we can consider them shorted, as they are considered ideal. The equivalent circuit will be  $V_{dc}$ , with the output voltage named  $v_o$  being the one on. When the current direction is positive, the current flows through the transistor and back to the load. When the current direction is opposite, the current flows through the diodes and back to the load. When the current is negative, the current flows through the diode and back to the load.

The voltage across nonconducting devices must withstand  $V_{dc}$  because it is shorted to  $V_{dc}$ . Non-conducting devices must block  $V_{dc}$  and shorted  $V_{dc}$ , while conducting devices carry the current  $i_o$ . This is important to remember, as we will use this information when drawing waveforms. In conclusion, the H bridge converter is a versatile and versatile converter that can be used in various applications. It has four IGBTs and four antiparallel diodes, with the potential for additional configurations depending on the application. By understanding the

different switching combinations and their equivalent circuits, we can better understand the design principles and applications of the H bridge converter.

On discussing the concept of pulse width modulation (PWM) in the context of H bridge converters. Focuses on four equivalent circuits, each representing a different type of current flow. The first circuit is called Vo, where the current is positive and flows downward to the negative terminal and positive to the positive terminal. The voltage is represented by  $Vo = -Vdc$  and  $Idc = -Io$ . When the current direction ( $Io$ ) is positive, the devices that conduct are Da- and Db+. In contrast, when  $Io$  is negative, it flows in the opposite direction, carrying the devices Ta- and Tb+. The third switching combination is Vo, where both upper switches are turned on. The voltage is represented by  $Vo = 0$  and  $Idc = 0$ . When the current direction is positive, the devices that conduct are Da+ and Tb+. When  $Io$  is negative, the conducting devices are Db+ and the diode Da+. The blocking voltages for non-conducting devices remain constant at  $Vdc$ . The fourth equivalent circuit is Ta- and Tb-, where the lower two switches are on. The path is followed by  $Vo = 0$  and  $Idc = 0$ . When the current is positive, it flows downwards, while when it is negative, it flows upward. The gate pulse, also known as the gate pulse, is given to the gate of the IGBT or MOSFET.

As explained earlier there are two main types of PWM for H bridge converters: bipolar PWM, which uses the diagonal combinations Ta+ and Tb+, and unipolar PWM, which uses all four switching combinations. The modulation method used affects the voltage and current waveforms in different components and the design process. If the waveform changes, the device must withstand voltage, current, and frequencies, which affects the design accordingly. The key points are that when considering multiple switching combinations for a converter, it is essential to analyze the equivalent circuits for each possible switching combination to determine the different voltages and currents flowing through different devices and components. This helps in determining device ratings during the design process.

## 4.3 Schematic Designing

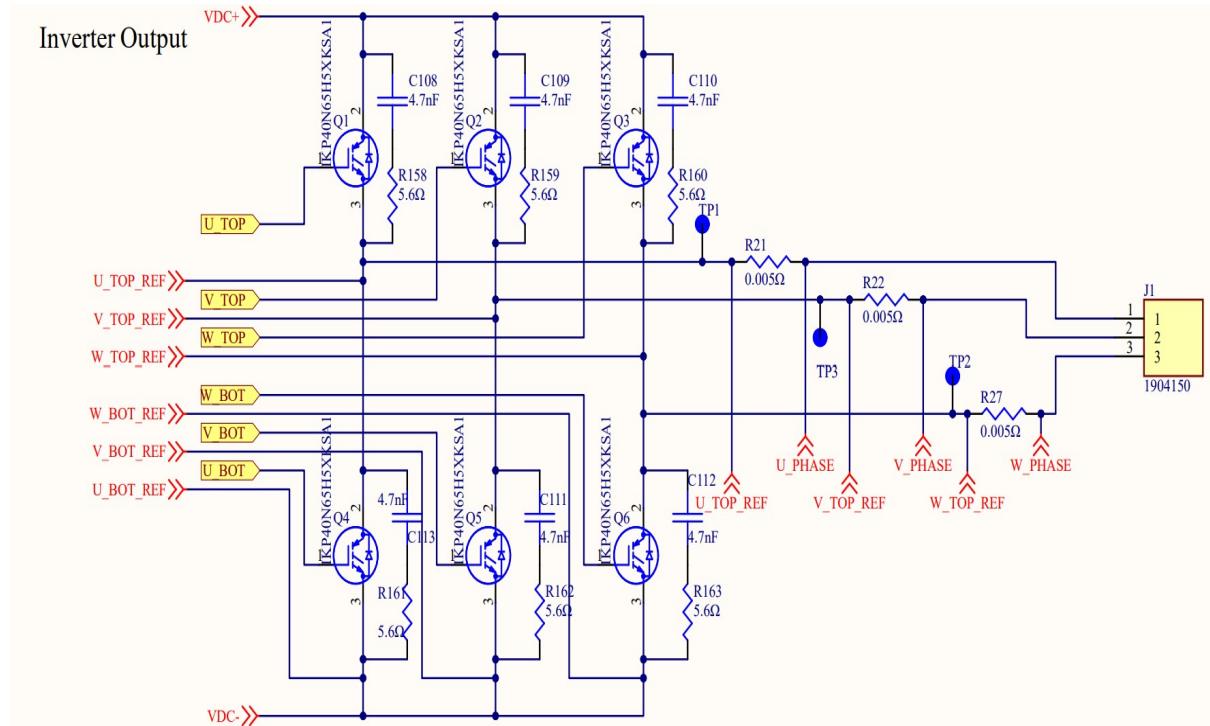

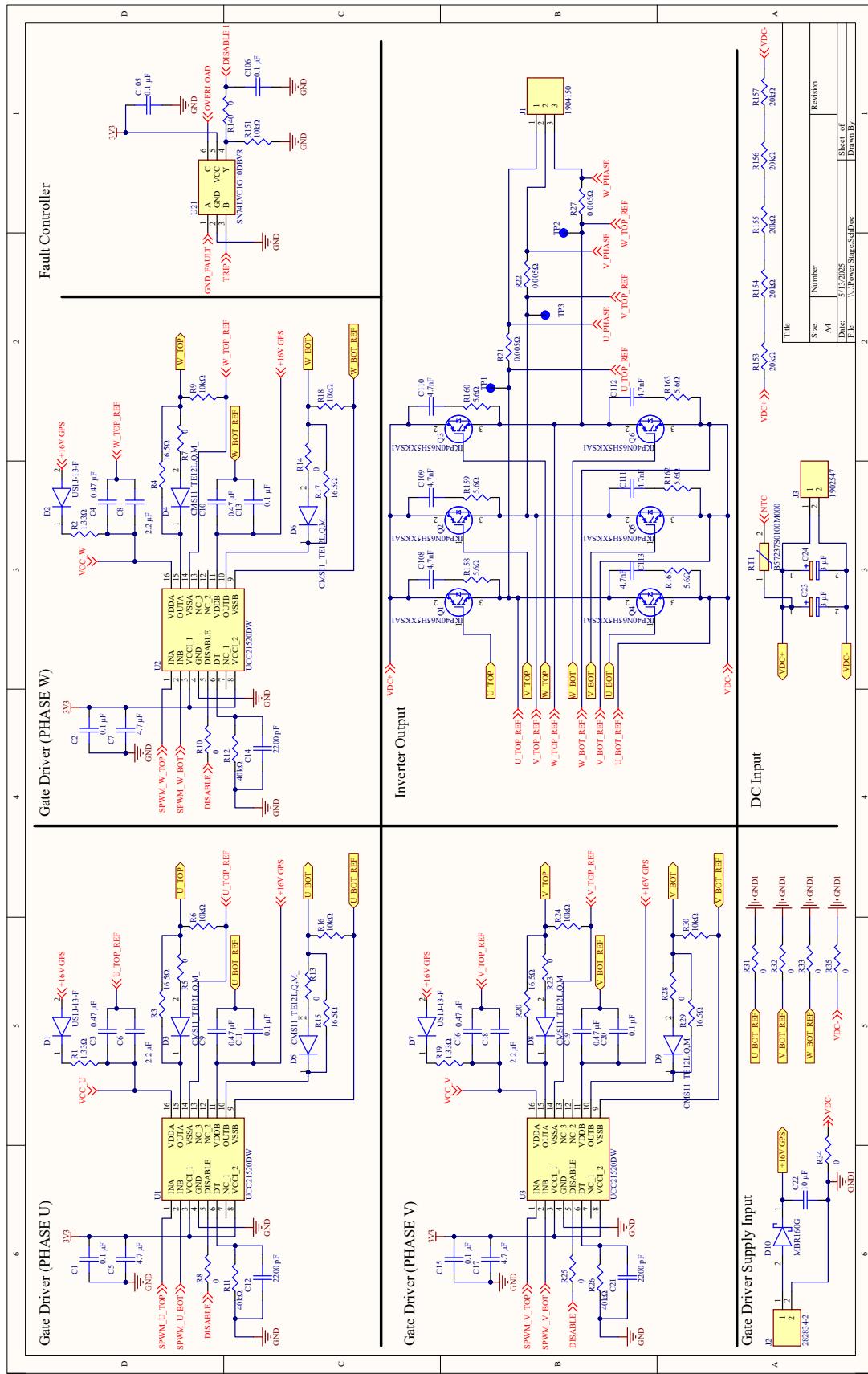

### 4.3.1 Power Stage Architecture

Figure 4.2: H - Bridge Design

The three-phase bridge inverter topology forms the core of modern power conversion systems. The six IGBTs (Q1-Q6) are arranged in a specific configuration to enable DC to AC conversion through controlled switching. The IKP40N65H5XKSA1 IGBTs used in this circuit are high-performance devices with several important characteristics.

- Voltage rating of 650V, suitable for industrial applications

- Low collector-emitter saturation voltage ( $V_{CE(sat)}$ ) to minimize conduction losses

- Fast switching capability to reduce switching losses

- Built-in anti-parallel freewheeling diodes to handle inductive load currents during commutation

The three half-bridge legs (U, V, W) operate with complementary switching - when the top switch is on, the bottom switch must be off, and vice versa. A small dead-time (typically a few microseconds) is implemented in the control signals to prevent shoot-through currents that

could damage the devices. Each leg generates one phase of the three-phase output, with the voltage at each output terminal switching between the positive and negative DC bus rails.

The physical layout of these components is critical, as they must be arranged symmetrically to ensure equal current distribution and thermal management. Power devices are typically mounted on heat sinks with thermal interface materials to dissipate the heat generated during operation.

1. DC Bus and Filtering: The DC bus structure is more sophisticated than might initially appear. The VDC+ and VDC- rails must maintain stable voltage during rapid current changes caused by switching events. The system typically includes the following.

- Large electrolytic bulk capacitors (not shown in the schematic) to store energy and maintain DC bus voltage

- Film capacitors placed close to the power modules for high-frequency decoupling

- The 4.7nF snubber capacitors (C108-C113) connected directly across each IGBT

These snubber capacitors serve specific purposes:

- Absorb energy stored in parasitic inductances during switching transitions

- Reduce voltage overshoot during turn-off, protecting the IGBTs from voltage spikes

- Slow down the rate of voltage change ( $dv/dt$ ) to reduce electromagnetic interference

- Redistribute switching losses to improve thermal management

The size of these capacitors requires careful consideration of the switching frequency, DC bus voltage, and specific characteristics of the power devices. Too small and they will not effectively suppress transients; too large and they can increase switching losses.

2. Output connection: The three-phase output connector J1 (1904150) represents the interface to the load. This connection requires careful consideration:

- The connector must be rated for the maximum current and voltage of the application

- Wire gauge selection must account for current capacity, voltage drop, and thermal considerations

In motor drive applications, the output may connect to additional components such as

- Common mode chokes to reduce electromagnetic interference

- dv/dt filters to protect motor insulation from voltage stress

- Sine wave filters to produce smoother output waveforms

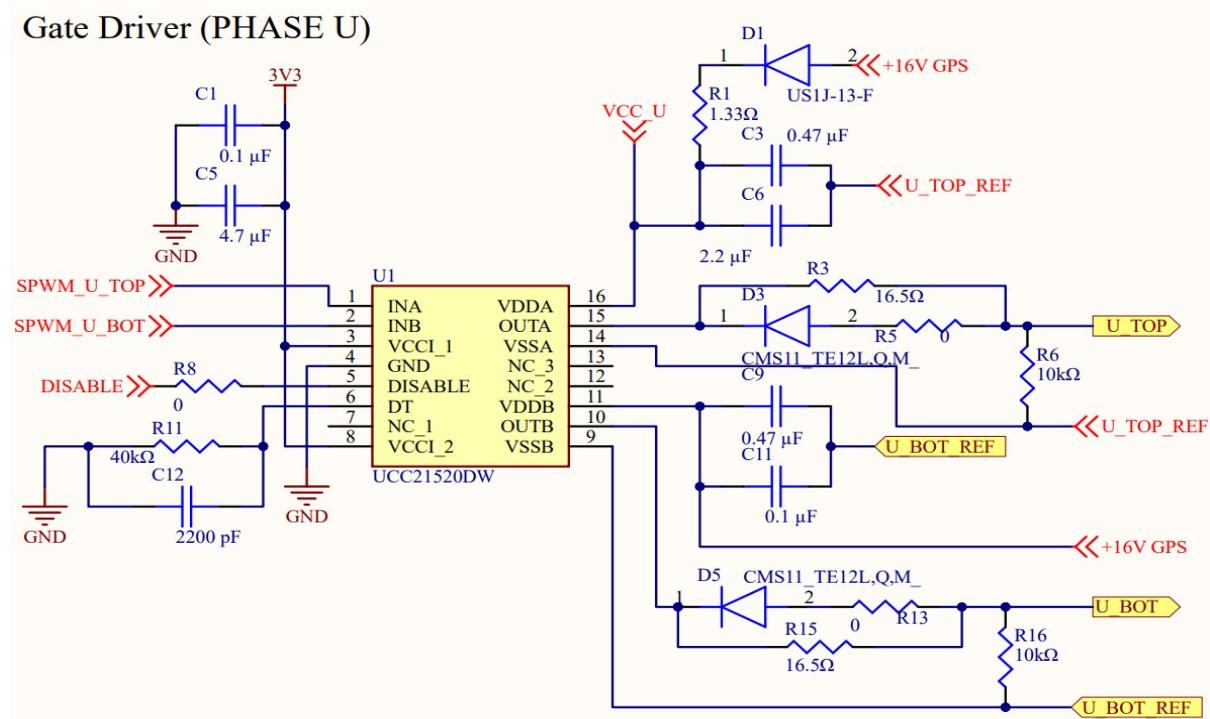

#### 4.3.2 Gate Drive and Control Signals

The schematic shows a gate driver circuit for Phase U of a three-phase inverter system. This circuit is responsible for properly driving the high-side (top) and low-side (bottom) power transistors in the inverter's Phase U leg. Identical circuits would be implemented for phases V and W in a complete three-phase system. The heart of the circuit is the integrated circuit

Figure 4.3: Gate Driver Design

UCC21520DW (U1), which is a dual-channel isolated gate driver specifically designed for high-voltage power switching applications. This IC provides the following.

- Galvanic isolation between the control signals and power stage

- Separate driving capability for both high-side and low-side switches

- Protection features to prevent shoot-through conditions

- High current drive capability for fast switching of power devices

The UCC21520DW has two input channels (INA and INB on pins 1 and 2) that receive the PWM control signals (SPWM\_U\_TOP and SPWM\_U\_BOT) from the controller. These signals determine the switching pattern of the power transistors. The outputs (OUTA and OUTB on pins 15 and 10) drive the gates of the power devices through additional circuitry.

### 1. Input Stage and Control:

The input side of the gate driver includes several important components:

- PWM Signal Inputs: SPWM\_U\_TOP and SPWM\_U\_BOT signals enter the circuit and connect directly to the INA and INB pins of the UCC21520DW.

- Disable Function: A DISABLE signal connects to pin 5 through R8 ( $0\Omega$ ), allowing the controller to disable both outputs simultaneously for safety or during fault conditions.

- Input Power Supply: The circuit is powered by a 3V3 supply connected to capacitors C1 (0.1) and C5 (4.7), which provide filtering and decoupling.

- Dead-Time Control: The DT pin (pin 7) is connected to a timing network consisting of R11 ( $40k\Omega$ ) and C12 (2200pF). This RC network sets the dead-time between the top and bottom switching signals to prevent shoot-through currents.

### 2. Output Stage and Gate Drive:

The output stage for each switch contains several components:

#### i. High-Side (Top) Switch Drive Circuit:

- Isolation diode: D3 (CMS11\_TE12L\_QM) prevents reverse current flow

- Gate Resistor: R3 ( $16.5\Omega$ ) controls the turn-on/turn-off speed of the power transistor, balancing switching speed with noise and EMI considerations

- Zero-Ohm Resistor: R5 ( $0\Omega$ ) serves as a jumper that could be replaced with a resistor if needed for tuning the circuit

- Pull-Down Resistor: R6 ( $10k\Omega$ ) ensures that the gate remains at a defined potential when not actively driven

- Feedback Network: The U\_TOP\_REF signal provides feedback to the control system.

#### ii. Low-Side (Bottom) Switch Drive Circuit:

- Isolation diode: D5 (CMS11\_TE12L\_QM) prevents reverse current flow

- Gate Resistor: R15 ( $16.5\Omega$ ) controls switching characteristics

- Zero-Ohm Resistor: R13 ( $0\Omega$ ) serves as a jumper

- Pull-Down Resistor: R16 ( $10k\Omega$ ) ensures a defined gate potential when not driven

- Feedback Network: The U\_BOT\_REF signal provides feedback to the control system.

### 3. Power Supply and Filtering

The circuit includes sophisticated power supply and filtering components:

#### i. High-Side Power Supply:

- VCC\_U supplies power to the high-side driver circuitry

- D1 (US1J-13-F) rectifies the +16V GPS supply

- R1 ( $1.33\Omega$ ) limits inrush current

- C3 ( $0.47\mu F$ ) and C6 ( $2.2\mu F$ ) filter the supply voltage

#### ii. Output Filtering:

- C9 ( $0.47\mu F$ ) and C11 ( $0.1\mu F$ ) provide filtering for the low-side driver output

- These capacitors help reduce noise and ensure clean switching signals

### 4. Generalized Implementation for the Three-Phase System

In a complete three-phase inverter system, this gate driver circuit would be replicated three times, one for each phase (U, V and W). The only differences would be the signal names:

- Phase U: SPWM\_U\_TOP, SPWM\_U\_BOT, U\_TOP, U\_BOT, U\_TOP\_REF, U\_BOT\_REF, VCC\_U

- Phase V: SPWM\_V\_TOP, SPWM\_V\_BOT, V\_TOP, V\_BOT, V\_TOP\_REF, V\_BOT\_REF, VCC\_V

- Phase W: SPWM\_W\_TOP, SPWM\_W\_BOT, W\_TOP, W\_BOT, W\_TOP\_REF, W\_BOT\_REF, VCC\_W

### 5. Technical Considerations and Design Rationale

- Isolation strategy: The UCC21520DW provides reinforced galvanic isolation between the control circuitry and the power stage, which is critical for safety and noise immunity. This isolation protects the low-voltage control electronics from the high voltages present in the power stage.

- Dead-Time Implementation: The dead-time circuit (R11 and C12) ensures that both the high-side and the low-side switches are never on simultaneously, preventing destructive shoot-through currents. The  $40k\Omega$  resistor and  $2200pF$  capacitor create a time constant that determines the minimum delay between the switching transitions.

- Gate Drive Optimization: The  $16.5\Omega$  gate resistors (R3 and R15) are carefully selected to balance:

- Switching speed (faster switching reduces losses but increases EMI)

- Gate current peaks (limited to protect the driver IC)

- Ringing and oscillation (damped to prevent false triggering)

- Thermal Considerations: The zero ohm resistors (R5 and R13) allow for future adjustment if thermal testing indicates the need to slow down the switch to reduce losses.

- Feedback Implementation: The reference signals (U\_TOP\_REF and U\_BOT\_REF) provide feedback to the control system for monitoring and protection purposes. These signals can be used to detect fault conditions such as short circuits or open circuits.

- Power Supply Filtering: Multiple capacitors with different values (0.1, 0.47, 2.2, 4.7) are used to filter different frequency ranges of noise, ensuring stable operation throughout the frequency spectrum.

This gate driver design represents a robust and industry-standard approach to driving power semiconductors in three-phase inverter applications, with careful attention to isolation, protection, switching performance, and noise immunity.

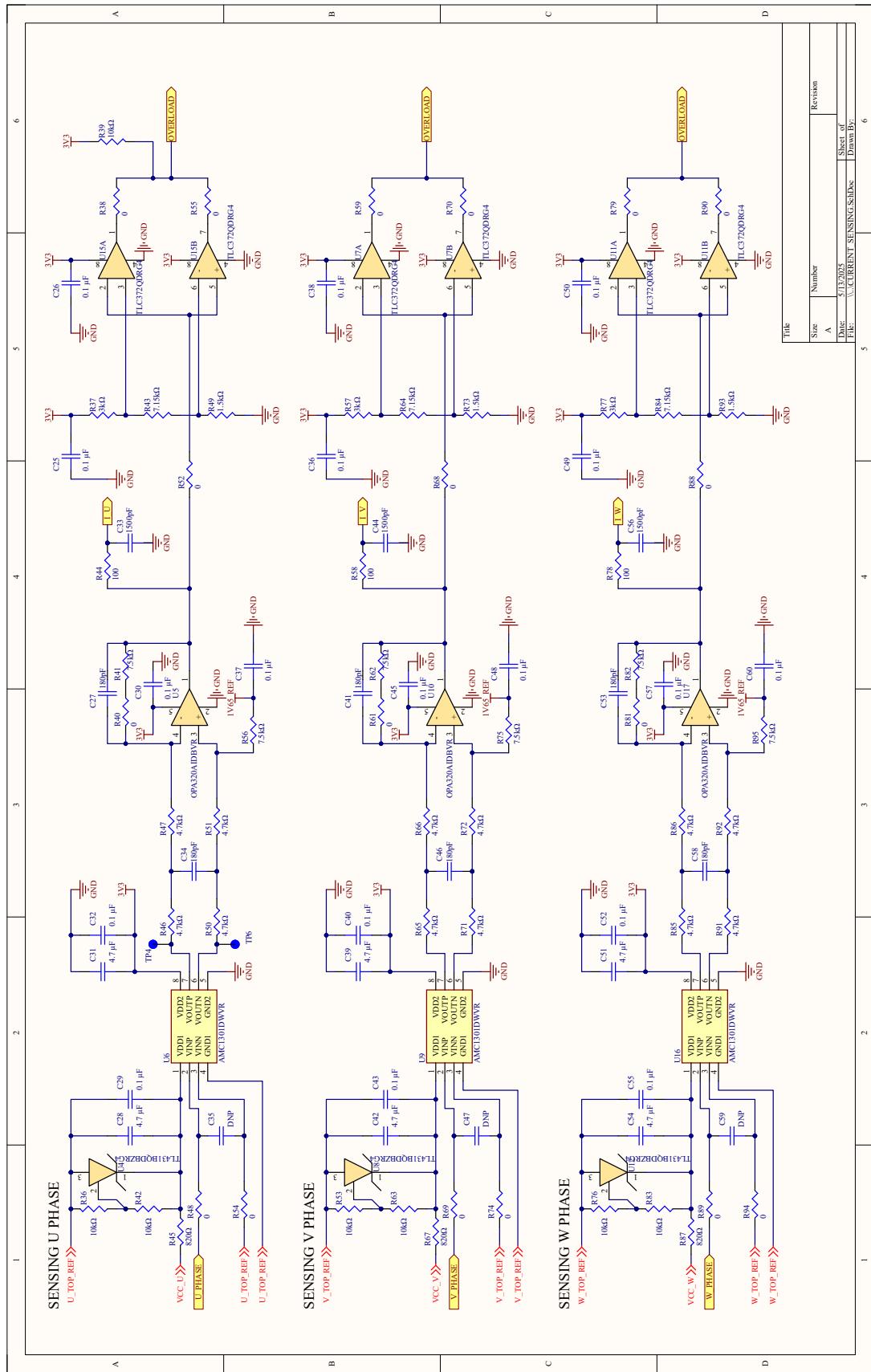

### 4.3.3 Current Sensing

The schematic shows a sophisticated current sensing circuit for Phase U of a three-phase inverter system. This circuit is designed to accurately measure the current flowing through the

power stage and provide protection against over-current conditions. An identical circuit would be implemented for phases V and W in a complete three-phase system.

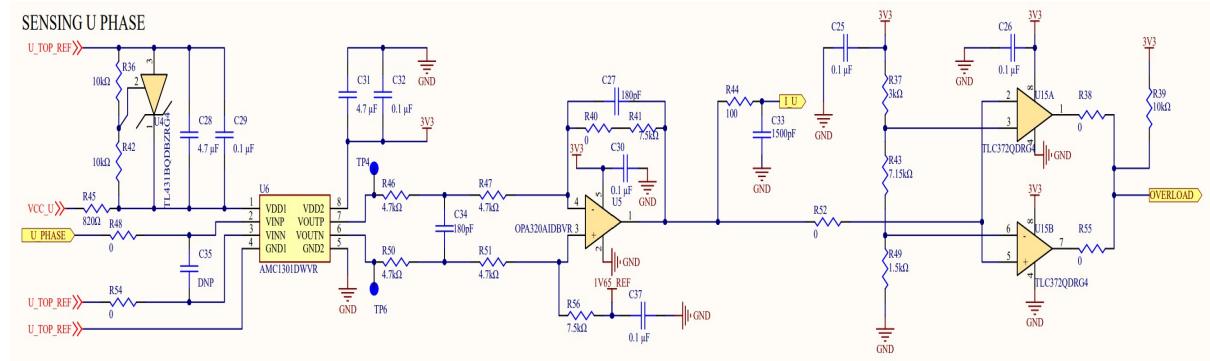

Figure 4.4: Current Sensing Circuit

### 1. Input Stage and Signal Conditioning

The circuit begins with the U\_TOP\_REF and U\_PHASE input signals that represent the voltage across the current sensing shunt resistor in the power stage. These signals enter through two paths:

#### i. Differential Amplifier Input:

- U\_TOP\_REF connects through a  $10k\Omega$  resistor (R41) to the non-inverting input

- U\_PHASE connects through a  $0\Omega$  resistor (R48) to the AMC1301DWVR isolation amplifier

#### ii. Buffer Stage:

- U\_TOP\_REF also connects through a  $10k\Omega$  resistor (R42) to a TL431AIDBZR2G precision shunt regulator (U2)

- This creates a buffered reference signal

The TL431AIDBZR2G (U2) acts as a voltage reference and buffer, with supporting components:

- $10k\Omega$  resistors (R41, R42) for biasing

- Decoupling capacitors C28 (4.7) and C29 (0.1) for stable operation

- VCC\_U supplies power to this stage

## 2. Isolation Amplifier Stage

At the core of the sensing circuit is the AMC1301DWVR (U6), a precision isolated amplifier specifically designed for current shunt measurement in high-voltage systems. This component:

- Provides galvanic isolation between the power circuit and control electronics

- Has high common-mode rejection for accurate measurements in noisy environments

- Features a differential input for connecting across the shunt resistor

The AMC1301 connections include:

- VIN+ and VIN- (pins 2 and 3) for differential input

- VOUT+ and VOUT- (pins 7 and 6) for differential output

- VDD1 and GND1 (pins 1 and 4) for input-side power

- VDD2 and GND2 (pins 8 and 5) for output-side power

Power and filtering components include:

- C31 (4.7F) and C32 (0.1F) for input-side power filtering

- C35 (DNP - Do Not Populate) placeholder for additional filtering if needed

- 3V3 supply powers the output side of the isolation barrier

## 3. Differential to Single-Ended Conversion

The differential output of the isolation amplifier is converted to a single-ended signal using an OPA320AIDBVR3 (U7) precision operational amplifier configured as a differential amplifier:

- R46 and R47 (both  $4.7k\Omega$ ) connect to the differential outputs of the AMC1301

- R50 and R51 (both  $4.7k\Omega$ ) provide feedback and set the gain

- C34 is connected across R50 to form a low-pass filter, reducing high-frequency noise

- Test points TP4 and TP6 allow for signal measurement during testing and calibration

The OPA320AIDBVR3 features the following:

- Low noise for accurate signal reproduction

- High precision for reliable current measurement

- Rail-to-rail output for maximum dynamic range

#### 4. Reference and Filtering

The circuit includes a reference voltage generation section:

- R56 ( $7.5k\Omega$ ) and C37 ( $0.1\mu F$ ) create a filtered reference voltage (VGCC\_REF)

- C30 ( $0.1\mu F$ ) provides additional filtering for the op-amp

- C27 (180pF) and R44 ( $10\Omega$ ) form an RC filter to reduce high-frequency noise

#### 5. Comparison stage for overcurrent protection

The final section features two TLC372QDRG4 comparators (U15A and U15B) that implement overcurrent protection.

##### i. First Comparator (U15A):

- The processed current signal connects to the inverting input (pin 2)

- A reference threshold set by R37 ( $2k\Omega$ ) and R43 ( $7.15k\Omega$ ) connects to the non-inverting input (pin 3)

- Output (pin 1) connects through R38 ( $0\Omega$ ) to the second comparator

##### ii. Second comparator (U15B):

- Input from the first comparator connects to the non-inverting input (pin 5)

- R49 ( $1.5k\Omega$ ) provides positive feedback for hysteresis

- Output (pin 7) provides the OVERLOAD signal to the control system

Supporting components include:

- C25, C26 (both  $0.1\mu F$ ) for the decoupling of the power supply

- R39 ( $10k\Omega$ ) as a pull-up resistor

- R52 and R55 (both  $0\Omega$ ) allow for circuit tuning if needed

6. Generalized Implementation for the Three-Phase System In a complete three-phase inverter system, this sensing circuit would be replicated three times with identical component values but different signal names:

- Phase U: U\_TOP\_REF, U\_PHASE, VCC\_U

- Phase V: V\_TOP\_REF, V\_PHASE, VCC\_V

- Phase W: W\_TOP\_REF, W\_PHASE, VCC\_W

Each phase would have its own OVERLOAD signal that could be combined in the control system to trigger appropriate protective actions.

## 7. Technical Design Considerations

- Isolation strategy: The AMC1301 provides reinforced galvanic isolation (up to 7kV) between the high-voltage power stage and low-voltage control electronics, protecting the control system and ensuring measurement accuracy.

- Precision Measurement: The combination of precision components ensures accurate current measurement:

- The AMC1301 has a typical gain error of less than 0.5%

- The OPA320 has a low offset voltage (typically  $<150\mu\text{V}$ )

- Matched resistor values maintain balanced differential signal paths

- Noise Immunity: Multiple filtering stages reduce measurement noise:

- input and output decoupling capacitors

- strategic placement of bypass capacitors RC filters at critical nodes

- differential signaling throughout most of the circuit

- Overcurrent protection: The dual-comparator design with hysteresis provides reliable overcurrent detection with:

- Fast response time (typically  $<1\mu\text{s}$ )

- Adjustable threshold via resistor values

- Hysteresis to prevent oscillation at the threshold boundary

- Direct OVERLOAD signal output for immediate protective action

- Layout Considerations: Though not visible in the schematic, the physical implementation would require:

- Careful separation of high-voltage and low-voltage sections

- Short traces for high-frequency signals

- Proper grounding to prevent ground loops

- Shielding to minimize electromagnetic interference

This current sensing circuit represents a professional-grade design that balances accuracy, noise immunity, and protection capabilities, essential for the reliable operation of high-power three-phase inverter systems in industrial applications, motor drives, or renewable energy systems.

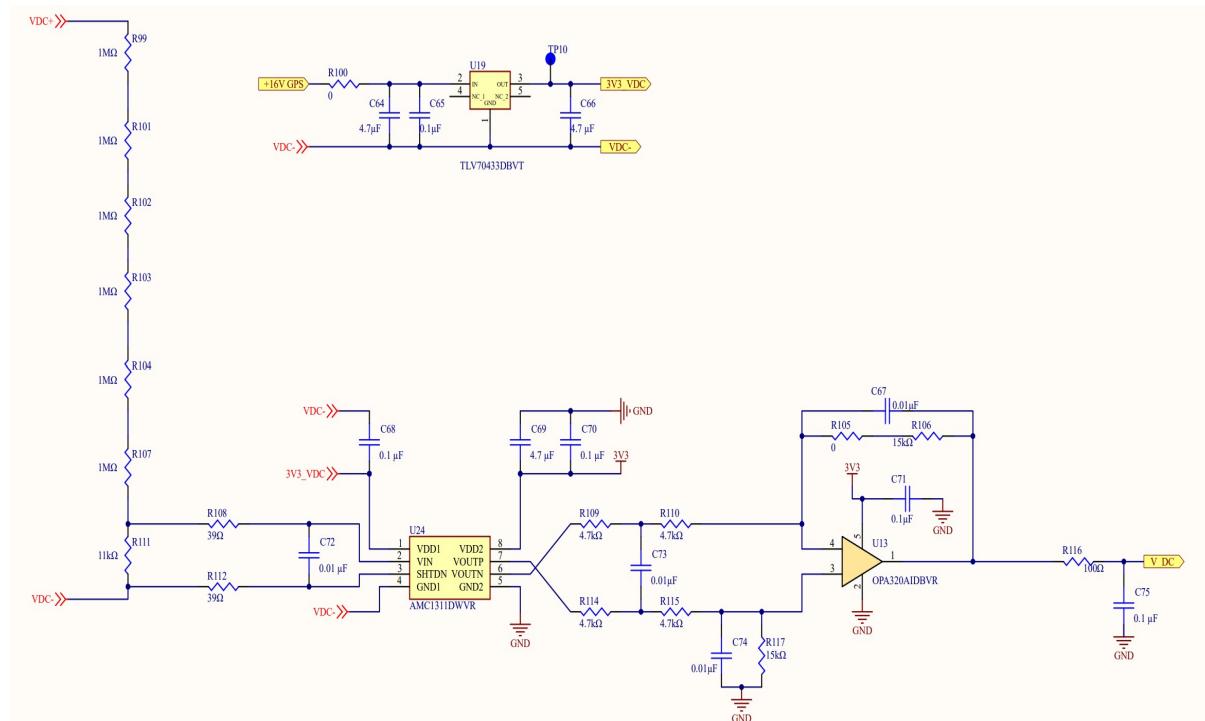

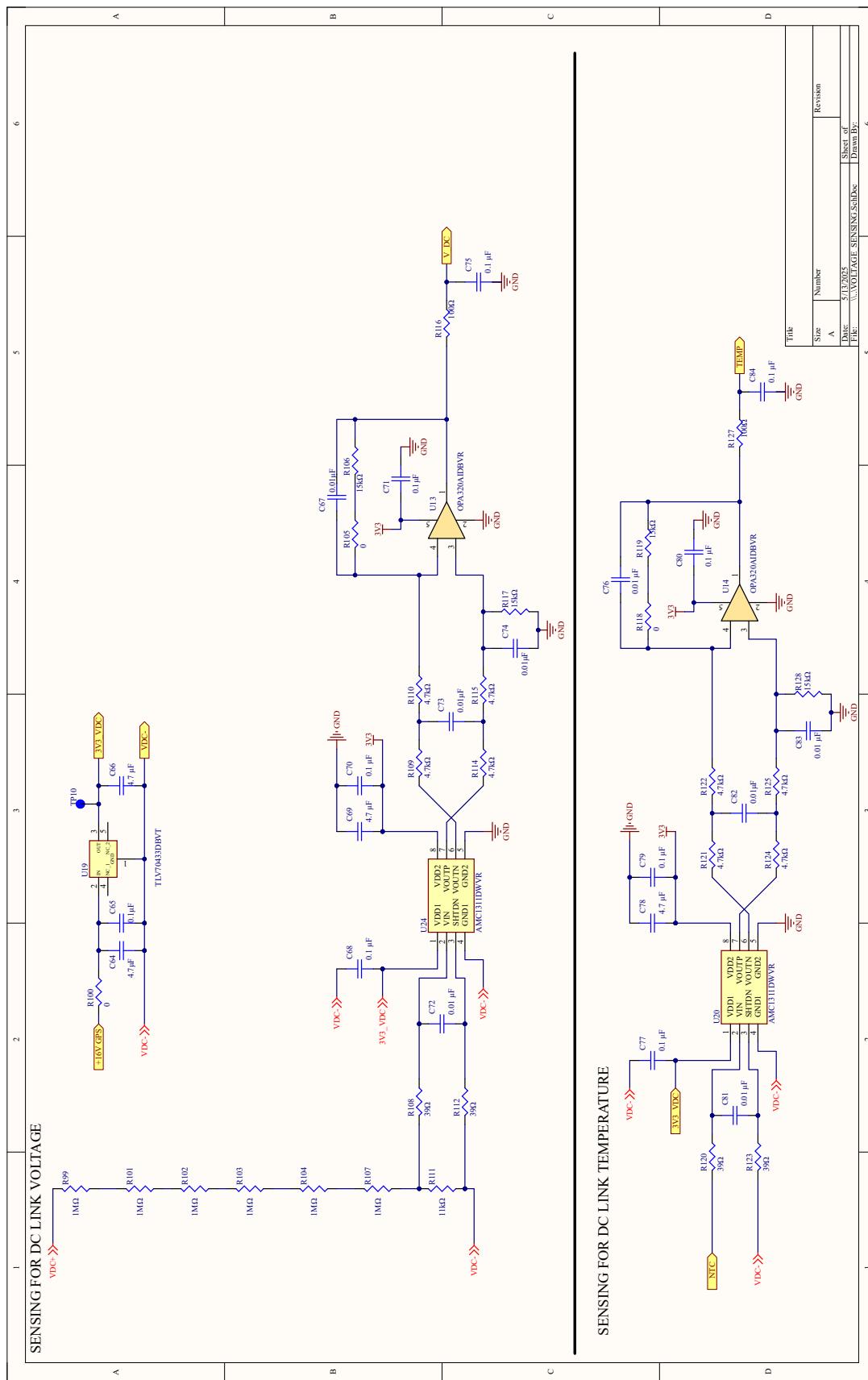

#### 4.3.4 Sensing circuit for DC Link Voltage

The schematic shows a sophisticated DC link voltage sensing circuit designed for a three-phase inverter system. This circuit provides accurate measurement of the high voltage DC bus while maintaining galvanic isolation between the power stage and control electronics.

Figure 4.5: DC Link Voltage Sensing Circuit

### 1. Voltage Divider Network

The left side of the schematic features a high-impedance voltage divider network consisting of:

- Six  $1M\Omega$  resistors (R99, R101, R102, R103, R104, R107) connected in series

- An  $11k\Omega$  resistor (R111) at the bottom of the divider chain

This resistor network scales the high DC link voltage (VDC +) to a manageable level for the isolation amplifier. The high total resistance ( $6M\Omega + 11k\Omega$ ) ensures minimal loading on the DC bus while providing appropriate voltage division. The design uses multiple high-value resistors in series rather than a single resistor to distribute the voltage stress and improve reliability in high-voltage applications.

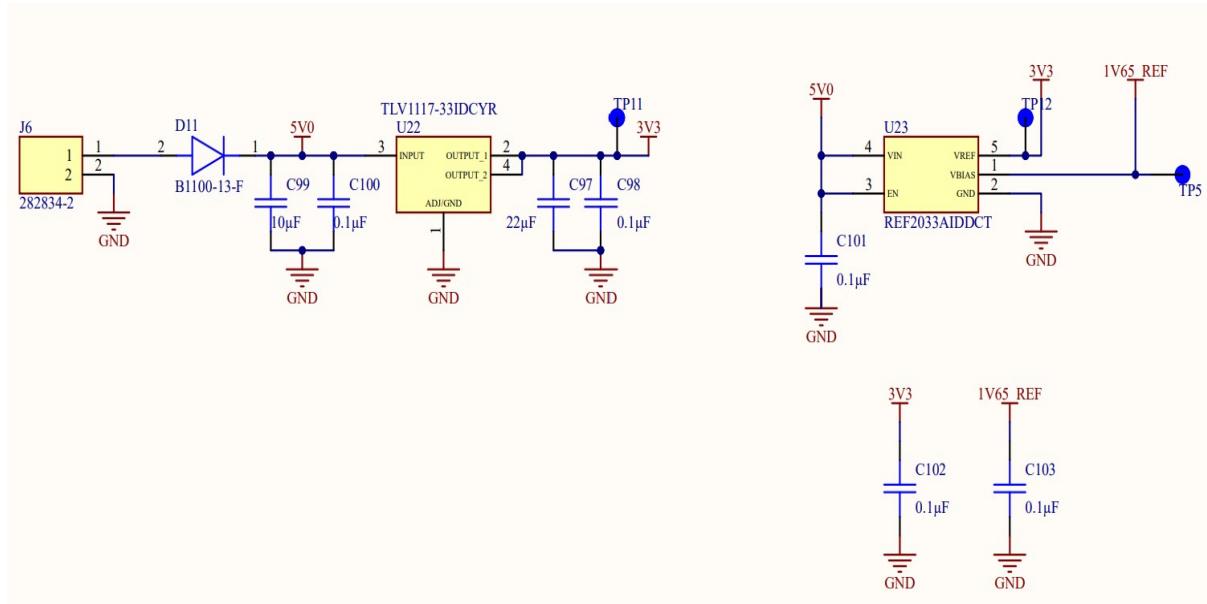

### 2. Power Supply Section

At the top of the schematic, there is a power supply section built around the TLV70433DBVT low-dropout regulator (U19):

- Input: +16V GPS (Gate Power Supply)

- Output: 3V3\_VDC (3.3V regulated supply)

- R100 ( $0\Omega$ ) serves as a jumper or current-limiting option

- Input filtering: C64 ( $4.7\mu F$ ) and C65 ( $0.1\mu F$ ) capacitors

- Output filtering: C66 ( $4.7\mu F$ ) capacitor

- Test point TP10 allows voltage measurement during testing

This regulated 3.3V supply powers the isolation and signal conditioning components.

### 3. Isolation Amplifier Stage

The core of the sensing circuit is the AMC1311DWVR (U24), a precision isolated delta sigma modulator specifically designed for voltage sensing in high-voltage systems.

- VDD1 (pin 1) and GND1 (pin 4) connect to the high-voltage side

- VDD2 (pin 8) and GND2 (pin 5) connect to the isolated low-voltage side

- VIN (pin 2) receives the divided down DC-link voltage

- SHDN (pin 3) is the shutdown input (connected to VDC-)

- VOUTP (pin 6) and VOUTN (pin 7) provide differential output signals

#### 4. Power filtering components include:

- C68 ( $0.1\mu\text{F}$ ) on the high-voltage side

- C69 ( $4.7\mu\text{F}$ ) and C70 ( $0.1\mu\text{F}$ ) on the low-voltage side

#### 5. Differential to Single-Ended Conversion

The differential output from the isolation amplifier is converted to a single-ended signal using an OPA320AIDBVR (U13) precision operational amplifier configured as a differential amplifier:

- R109 and R110 (both  $4.7k\Omega$ ) connect to the differential outputs of the AMC1311

- R114 and R115 (both  $4.7k\Omega$ ) provide feedback and set the gain

- C73 ( $0.01\mu\text{F}$ ) provides filtering

- R117 ( $15k\Omega$ ) and C74 ( $0.01\mu\text{F}$ ) form an additional filter network

- R105 ( $0\Omega$ ) and R106 ( $15k\Omega$ ) set up the reference level

- C67 ( $0.01\mu\text{F}$ ) provides additional filtering

- R116 ( $10k\Omega$ ) and C75 ( $0.1\mu\text{F}$ ) form an output filter

#### 6. Signal Conditioning and Buffering

The final output stage includes:

- C71 ( $0.1\mu\text{F}$ ) for power supply decoupling of the op-amp

- Output labeled V\_DC represents the conditioned DC-link voltage signal ready for the ADC input

#### 7. Technical Design Considerations

- Isolation strategy: The AMC1311 provides reinforced galvanic isolation between the high-voltage DC bus and low-voltage control electronics, protecting the control system and ensuring measurement accuracy. This isolation is critical for safety in high-power applications

- Precision Scaling: The resistor divider network is carefully designed to scale the DC-link voltage (which can be up to 1026V according to similar designs) down to the input range of the isolation amplifier (0-2V for optimal performance)

- Noise Immunity: Multiple filtering stages reduce measurement noise:

- Input and output decoupling capacitors

- Strategic placement of bypass capacitors

- RC filters at critical nodes

- Differential signaling throughout most of the circuit

- High Input Impedance: The  $6M\Omega$  total resistance of the divider network ensures minimal loading on the DC bus, which is important for accurate voltage measurement and efficiency

- Protection Features: Although not explicitly shown, high-value resistors in the divider network provide inherent current limiting in the event of faults. In some implementations, Zener diodes would be added in parallel with some resistors for overvoltage protection.

This DC link voltage sensing circuit represents a professional-grade design that balances accuracy, safety through isolation, and noise immunity. It is essential for proper control and protection of the inverter system, enabling functions such as over-voltage protection, under-voltage detection, and precise control of power conversion processes.

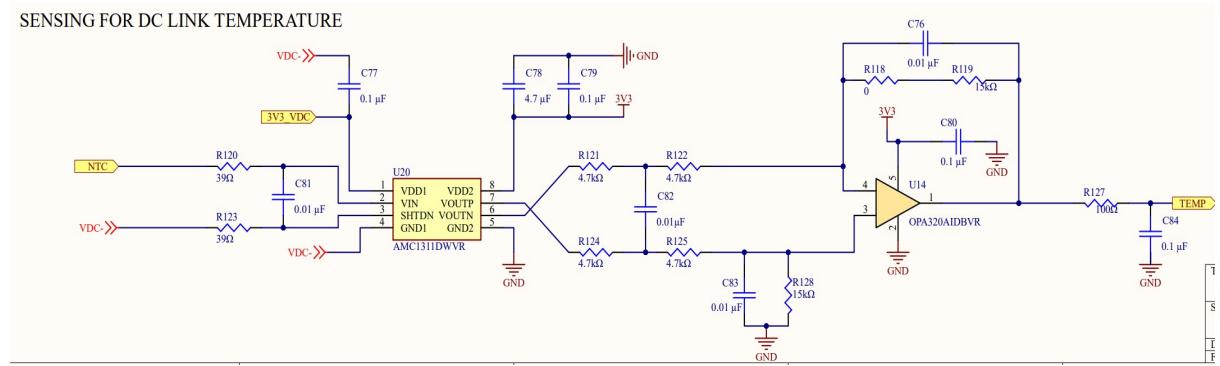

#### 4.3.5 DC LINK TEMPERATURE SENSING CIRCUIT

The schematic shows a sophisticated DC link temperature sensing circuit designed to accurately measure the temperature of the DC bus in a power electronics system while maintaining galvanic isolation between the power stage and control electronics.

##### 1. Input Stage and NTC Interface

The circuit begins with an NTC (Negative Temperature Coefficient) thermistor input on the left side. This thermistor is the actual temperature sensing element physically mounted on the DC link capacitor or bus bar. Key components in this stage include:

- Two  $39\Omega$  resistors (R120 and R123) connected in series with the NTC thermistor input

- A  $0.01\mu\text{F}$  capacitor (C81) for noise filtering at the input

Figure 4.6: DC Link Voltage Sensing Circuit

- The NTC thermistor's resistance varies inversely with temperature, providing the primary sensing function

This configuration allows the circuit to read the resistance change of the NTC thermistor, which is directly correlated to the temperature changes in the DC link.

## 2. Isolation Amplifier Stage

At the core of the sensing circuit is the AMC1311DWVR (U20), a precision isolated delta-sigma modulator specifically designed for voltage sensing with galvanic isolation:

- VDD1 (pin 1) and GND1 (pin 4) connect to the high-voltage side

- VDD2 (pin 8) and GND2 (pin 5) connect to the isolated low-voltage side

- VIN (pin 2) receives the voltage signal from the NTC thermistor network

- SHDN (pin 3) is the shutdown input (connected to VDC-)

- VOUTP (pin 6) and VOUTN (pin 7) provide differential output signals

The isolation amplifier is powered by:

- 3V3\_VDC supply on the high-voltage side with C77 (0.1 $\mu$ F) for filtering

- 3V3 supply on the low-voltage side with C78 (4.7 $\mu$ F) and C79 (0.1 $\mu$ F) for filtering

This isolation barrier is crucial for safety, separating the high-voltage power circuit from the low-voltage control electronics.

## 3. Differential to Single-Ended Conversion

The differential output from the isolation amplifier is converted to a single-ended signal using a precision signal conditioning network:

- Four  $4.7k\Omega$  resistors (R121, R122, R124, R125) form a differential amplifier configuration.

- C82 (0.01 $\mu$ F) provides filtering for the differential signal

- R128 ( $15k\Omega$ ) and C83 (0.01 $\mu$ F) form an additional filter network

#### 4. Signal Conditioning and Amplification

The final stage uses an OPA320AIDBVR (U14) precision operational amplifier configured as a non-inverting amplifier:

- The op-amp is powered by the 3V3 supply with C80 (0.1 $\mu$ F) for power supply decoupling

- R118 ( $0\Omega$ ) serves as a jumper

- R119 ( $1M\Omega$ ) provides high input impedance

- C76 (0.01 $\mu$ F) forms an input filter with R119

- The output is filtered by R127 ( $100\Omega$ ) and C84 (0.1 $\mu$ F)

- The final output is labeled T\_TEMP, representing the conditioned temperature signal

#### 5. Technical Design Considerations

- Isolation strategy: The AMC1311 provides reinforced galvanic isolation between the high-voltage DC link and low-voltage control electronics, protecting the control system and ensuring measurement accuracy. This isolation is critical for safety in high-power applications

- Temperature Measurement Principle: The circuit measures the voltage across the NTC thermistor, which changes with temperature. As the temperature increases, the thermistor's resistance decreases, altering the voltage division ratio in the input network.

- Noise Immunity: Multiple filtering stages reduce measurement noise:

- Input filtering with C81

- Power supply decoupling capacitors throughout the circuit

- Strategic RC filters at critical signal path points

- Differential signaling through the isolation barrier

- Signal Conditioning: The op-amp stage provides the following:

- Impedance matching between the isolation amplifier and subsequent ADC stages

- Additional filtering to improve signal quality

- Appropriate scaling of the temperature signal for the control system's input range

- Robustness: The  $39\Omega$  series resistors (R120 and R123) provide current limiting protection for the input stage, while the multiple filter capacitors enhance immunity to electrical noise in the harsh switching environment of power electronics.

This DC link temperature-sensing circuit represents a professional-grade design that balances accuracy, safety through isolation, and noise immunity. Temperature monitoring is essential for the protection of power components, as excessive temperatures can lead to premature failure or catastrophic breakdown of semiconductor devices and DC link capacitors. The circuit enables the control system to implement thermal protection algorithms, adjust switching patterns to reduce thermal stress, or shut down the system if temperatures exceed safe operating limits.

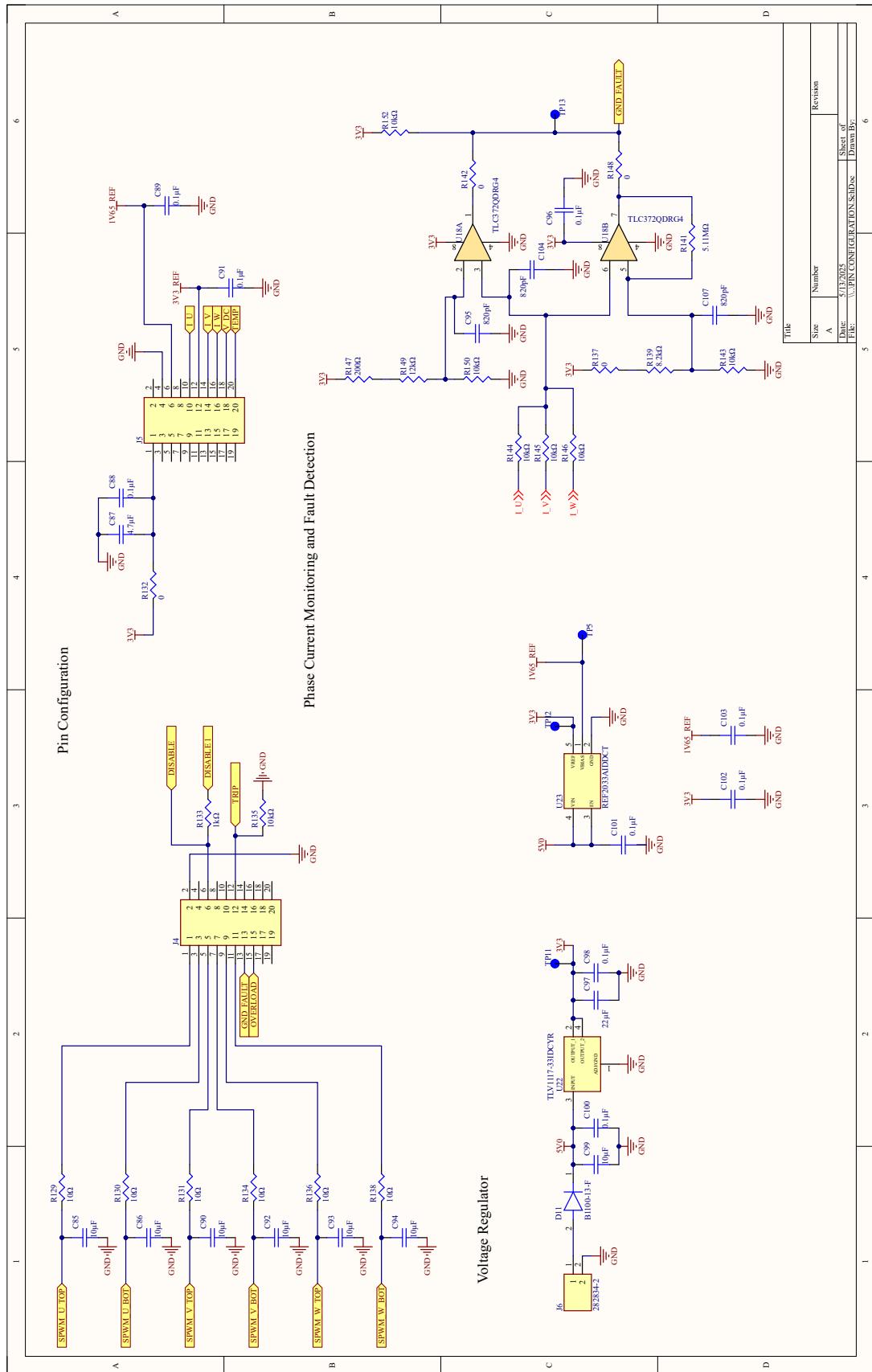

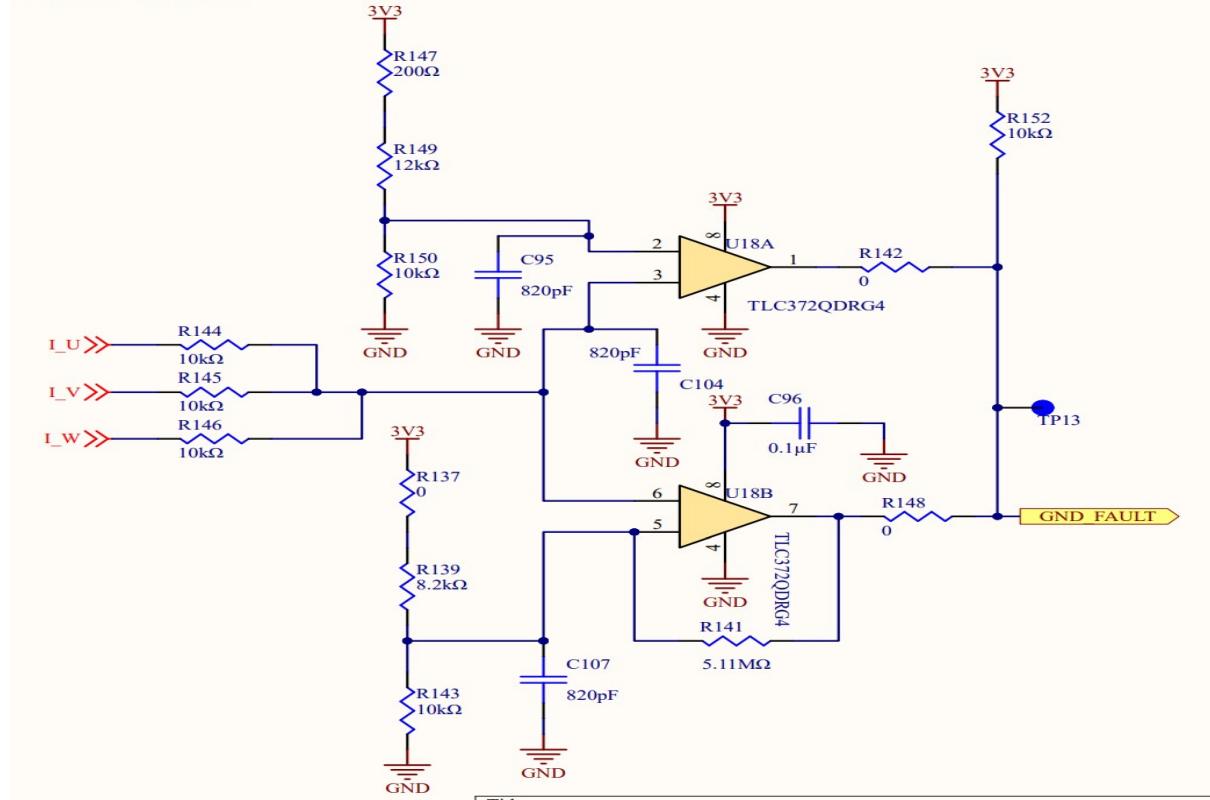

#### 4.3.6 Phase Monitoring and Fault Detection

The schematic shows a sophisticated ground fault detection circuit designed to monitor the three-phase currents ( $I_U$ ,  $I_V$ ,  $I_W$ ) in a power inverter system and detect imbalances that could indicate ground faults or other abnormal conditions. 1. Input Stage and Signal Summation

The circuit begins with three input signals representing the phase currents:

- $I_U$ : Phase U current signal

- $I_V$ : Phase V current signal

- $I_W$ : Phase W current signal

Each input signal passes through a  $10k\Omega$  resistor (R144, R145, R146) before being summed at a common node. This resistor network creates a signal averaging function that combines the three phase currents. In a balanced three-phase system with no ground fault, the sum of these currents should theoretically be zero (or very close to zero) due to Kirchhoff's Current Law.

## I Fault Detection

Figure 4.7: Phase Monitoring and Fault Detection Circuit

### 2. Upper Comparator Circuit (U18A)

The upper portion of the circuit features a TLC372QDRG4 comparator (U18A) with these key components:

#### i. Reference Voltage Divider:

- A voltage divider consisting of R147 ( $200\Omega$ ), R149 ( $12k\Omega$ ), and R150 ( $10k\Omega$ ) connected between 3V3 and ground

- This creates a precise reference voltage at the non-inverting input (pin 3)

#### ii. Input Filtering:

- C95 (820pF) capacitor provides noise filtering at the non-inverting input

- C104 (820pF) capacitor filters the inverting input (pin 2)

#### iii. Output Stage:

- R142 ( $0\Omega$ ) connects the output (pin 1) to the fault signal line

- R152 ( $10k\Omega$ ) serves as a pull-up resistor to 3V3

### 3. Lower Comparator Circuit (U18B)

The lower portion of the circuit features the second comparator in the TLC372 package (U18B):

#### i. Reference Voltage Divider:

- A voltage divider consisting of R137 ( $0\Omega$ ), R139 ( $8.2k\Omega$ ), and R143 ( $10k\Omega$ ) connected between 3V3 and ground

- This creates a second reference voltage at the non-inverting input (pin 5)

#### ii. Input Filtering:

- C107 (820pF) capacitor provides noise filtering at the non-inverting input

- C96 ( $0.1\mu F$ ) capacitor connected to 3V3 provides additional filtering

#### iii. Feedback Network:

- R141 ( $5.11M\Omega$ ) provides positive feedback for hysteresis, creating a Schmitt trigger configuration

- This prevents oscillation when the input signal is near the threshold

#### iv. Output stage:

- R148 ( $0\Omega$ ) connects the output (pin 7) to the GND\_FAULT signal line

- Test point TP13 allows for signal measurement during testing and debugging

### 4. Technical Operation and Design Considerations

- Fault Detection Principle: The circuit operates on the principle that in a balanced three-phase system, the sum of the three-phase currents should equal zero. Any significant deviation from zero indicates a potential ground fault or phase imbalance.

- Dual-threshold detection: The dual comparator arrangement creates a window comparator that can detect when the summed signal goes either above or below preset thresholds. This allows detection of both positive and negative imbalances in the three-phase system

- **Hysteresis Implementation:** The  $5.11M\Omega$  feedback resistor (R141) in the lower comparator creates hysteresis, which prevents the rapid osmotic movement of the fault signal when the input hovers near the threshold. The precise value ( $5.11M\Omega$ ) suggests a careful calculation to achieve specific hysteresis characteristics.

- **Noise Immunity:** Multiple filtering capacitors (820pF and 0.1 $\mu$  F) in strategic locations reduce the impact of switching noise. The resistor values are chosen to provide appropriate time constants for filtering while maintaining sensitivity.

- **Reference Voltage Precision:** The voltage divider networks are designed to create precise threshold voltages. The  $200\Omega/12k\Omega/10k\Omega$  and  $0\Omega/8.2k\Omega/10k\Omega$  combinations create different threshold levels for the upper and lower limits.

This ground fault detection circuit represents a professional-grade design that provides critical protection in three-phase power systems. By continuously monitoring the balance of phase currents, it can quickly detect ground faults or other abnormal conditions that could damage equipment or create safety hazards. The GND\_FAULT signal would typically connect to the system controller to trigger protective actions such as shutting down the inverter or activating alarms.

#### 4.3.7 DC Input Power Supply

The schematic shows a DC input circuit for a three-phase inverter system. This circuit represents the DC power entry point and includes temperature-sensing and connection components that form the foundation of the inverter's power stage.

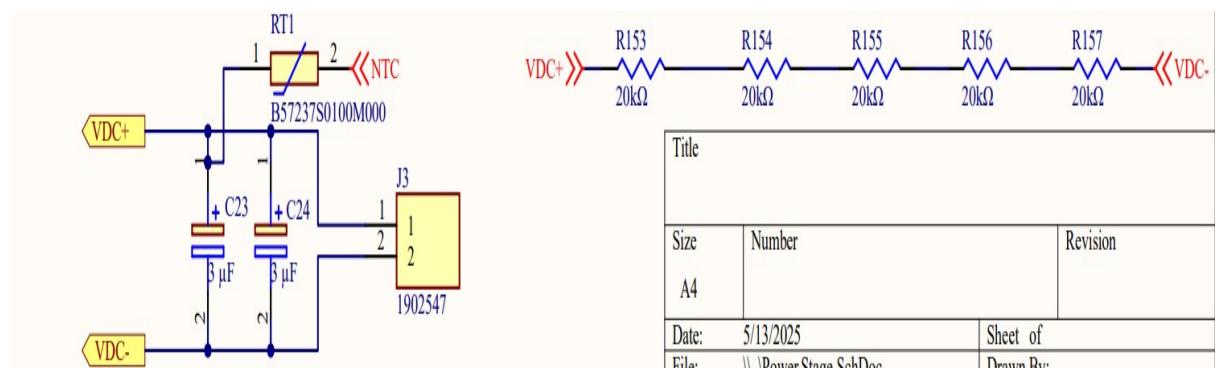

Figure 4.8: DC Power Supply Circuit

#### 1. DC Input Power Stage

The left side of the schematic shows the main DC power input section:

i. DC Bus Connections:

- VDC+ and VDC- terminals serve as the primary DC power input connections

- These terminals would connect to a DC power source such as batteries, a rectified AC supply, or solar panels

- The DC bus voltage would typically be in the range of several hundred volts for industrial inverters

ii. Filtering Capacitors: